# Structure of the interface in sub-nm EOT TmSiO/HfO2 gate stack

I.Z. Mitrovic<sup>1</sup>, <u>S.N. Supardan<sup>1</sup></u>, D. Hesp<sup>2</sup>, V.R. Dhanak<sup>2</sup>, S. Hall<sup>1</sup>, S. Schamm-Chardon<sup>3</sup>, E. Dentoni Litta<sup>4</sup>, P.-E. Hellström<sup>4</sup>, and M. Östling<sup>4</sup>

<sup>1</sup>Department of Electrical Eng. & Electronics; <sup>2</sup>Department of Physics, University of Liverpool, UK

<sup>3</sup>CEMES-CNRS and Université de Toulouse, Toulouse, France

<sup>4</sup>KTH Royal Institute of Technology, School of ICT, Sweden

Email of the corresponding author: nurbaya@liverpool.ac.uk

### **Abstract**

The scaling of the interfacial layer plays a central role in further advancement of high-k dielectric/metal gate CMOS technology. In this work, we focus on a high-k interfacial layer approach based on thulium silicate. A sub-nanometre scaled interfacial layer can be achieved via post deposition anneal at 550°C, which promotes the existence of a graded Tm-Si-O interface with strong sub-oxide Si 3+ presence.

### 1. Introduction

State-of-the-art CMOS technology employs HfO<sub>2</sub> due to its high dielectric constant (> 20) and ability to achieve suitable n- and p-MOSFET threshold voltages [1-4]. Hf-based dielectric is deposited on top of a subnm chemical oxide (SiOx) or oxynitride interfacial layer (IL), whose thickness can be controlled using different oxidation methods and carefully designed scavenging steps [2,3]. A general trend has been observed of strong degradation of the inversion layer mobility with decreased IL thickness, independent of the method used. Even stronger mobility and reliability degradation occurs if no IL is employed [4]. It has been demonstrated recently [1,6] that thulium silicate (TmSiO) is a contender for integration as a high-k IL, achieving equivalent oxide thickness (EOT) of the IL of  $\sim 2$ Å with interface state density  $<2\times10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>. An optimized annealing condition has been reported leading to gate leakage current density comparable with state-of-the-art SiOx/HfO<sub>2</sub> nFETs (0.7 A/cm<sup>2</sup> at gate bias of 1 V) at 0.6 nm EOT. However, there is no current understanding of the physical properties of this interface which can lead to the best-scaled gate stack. This paper addresses the latter and provides evidence of a graded IL with strong Si 3+ sub-oxide component.

## 2. Experimental

The TmSiO IL was formed via atomic layer deposition (ALD) of Tm<sub>2</sub>O<sub>3</sub> at 225°C, using TmCp<sub>3</sub> and H<sub>2</sub>O as precursors, on an HF-last Si surface and

annealing [6]. A silicate formation anneal was performed in N<sub>2</sub> at three different temperatures 550°C, 650°C and 750°C for 60 s, leading to the formation of a TmSiO/Tm<sub>2</sub>O<sub>3</sub> dielectric stack with a target physical thickness of the TmSiO layer of 0.9 nm, 1.3 nm and 2.1 nm respectively. Subsequently, the unreacted Tm<sub>2</sub>O<sub>3</sub> was removed selectively in H<sub>2</sub>SO<sub>4</sub>. HfO<sub>2</sub> was then deposited by ALD at 350°C, using Hf[C<sub>5</sub>H<sub>4</sub>(CH<sub>3</sub>)]<sub>2</sub>(OCH<sub>3</sub>)CH<sub>3</sub> and H<sub>2</sub>O as precursors, to a target physical thickness of 3 nm. Core level (CL) structure and the occupied density of states in the valence band were probed by x-ray photoelectron spectroscopy (XPS) using a SPECS monochromatic Al  $K\alpha$  x-ray source (hv = 1486.6 eV) operating at 200 W, and a PSP Vacuum Technology electron energy analyser. The atomic structure and elemental analysis were investigated on TiN capped samples using highresolution transmission electron microscopy (HRTEM) and electron energy-loss spectroscopy (EELS) performed on a field emission image-corrected FEI Tecnai<sup>TM</sup> F20 microscope operating at 200 kV.

# 3. Results & Discussion

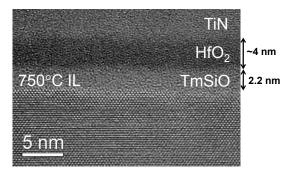

Fig. 1 shows an HRTEM image of a TmSiO/HfO<sub>2</sub> stack, with two amorphous layers with a bright (TmSiO) and a dark (HfO<sub>2</sub>) contrast. The thickness of the IL of  $\sim$ 2.2 nm is within the expected (2.1 nm) value from the annealing condition at 750°C. Figs. 2(a) and (b) show the XPS Tm 4d and Si 2p CL spectra for reference and TmSiO/HfO<sub>2</sub> samples. There is a clear

Figure 1. HRTEM image of TmSiO/HfO<sub>2</sub> gate stack with IL formed by post deposition anneal at 750°C.

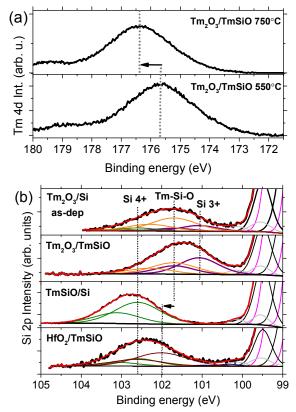

shift of the Tm 4d<sub>5/2</sub> peak position from 175.6 eV for sample with IL processed by post deposition anneal (PDA) at 550°C towards higher binding energies (BE) of 175.8 eV and 176.4 eV for 650°C and 750°C PDA samples, respectively (Fig. 2(a)). The latter is in agreement with forming a thicker IL (from 0.9 nm to 2.1 nm) as annealing temperature increases, and in line with that reported in the literature [7,8].

Figure 2. (a) XPS Tm 4d CLs for Tm<sub>2</sub>O<sub>3</sub>/TmSiO; (b) Si 2p CLs for TmSiO/HfO<sub>2</sub> stack with reference CLs for as-deposited Tm<sub>2</sub>O<sub>3</sub>/Si & TmSiO/Si (550°C PDA).

The XPS Si 2p spectrum is used in this study to resolve different bonds and the oxidation states of Si atoms in the IL via the chemical shift of the Si 2p core level. The spectrum is decomposed into the Si  $2p_{1/2}$  and Si  $2p_{3/2}$  spin-orbit partner lines (Fig. 2(b)). The spinorbit splitting and area ratio of 0.6 eV and 1:2 respectively were fixed for the fit [9]. The high BE side sub-peak from the mean substrate Si 2p<sup>0</sup> peak (Si 2p<sub>3/2</sub> @ 98.60 eV) gives a signature of the IL. It is evident from Fig. 2(b) that the centroid of the sub-peak is closest to the Si 2p<sup>0</sup> substrate peak for the sample after 550°C PDA and before etching of the remaining Tm<sub>2</sub>O<sub>3</sub> on top. The presence of the Tm-Si-O bond can be de-convoluted from the spectra at the chemical shift of 3.1 eV prior etching, and at 3.4 eV after etching and deposition of HfO<sub>2</sub>. The chemical shift of 3.6 eV has been reported for TmSiO from the Si 2s spectra [10]. Interestingly, a strong presence of the Si 3+ oxidation state at 2.48 eV chemical shift [9] is found, in particular for the stack processed at 550°C PDA. As the annealing temperature increases to 750°C, the intensity of Tm-Si-O component increases and Si 3+ component diminishes (not shown). The Si 4+ (i.e. SiO<sub>2</sub>) has a strong presence only in uncapped ILs likely to be due to their exposure to air prior XPS measurements.

## 4. Conclusion

We have given a quantitative structural analysis of the  $TmSiO/HfO_2$  interface using XPS, TEM and EELS techniques. The gate stacks were processed using three post deposition annealing temperatures from 550°C to 750°C. The best-scaled stack reveals a graded interface with a strong SiOx component.

## Acknowledgements

The research has received funding from the European Union 7th Framework Programme under Grant Agreement 312483 - ESTEEM2 (Integrated Infrastructure Initiative–I3).

## References

- [1] E. Dentoni Litta et al., IEEE TED 62(3) (2015) 934.

- [2] T. Ando, Materials 5(3) (2012) 478.

- [3] K. Choi et al., ECS Trans. 53(3) (2013) 17.

- $[4] \ L-A. \ Ragnarsson \ et \ al., \ Microel. \ Eng. \ 88(7) (2011) \ 1317.$

- [5] T. Kawanago et al., IEEE TED 59(2) (2012) 269.

- [6] E. Dentoni Litta et al., Solid-St. Electron. 98 (2014) 20.

- [7] T-M. Pan et al., J. Phys. Chem. C, 113 (2009) 21937.

- [8] T-M. Pan, L-C. Yen, Appl. Surf. Sci. 256 (2010) 2786.

- [9] F.J. Himpsel et al., Phys. Rev. B 38(9) (1988) 6084.

- [10] M. Kouda et al., J. Vac. Sci. Techn. B 29 (2011) 062202.