# Hafnium Oxide Based Gate Stacks on Germanium and Silicon

Thesis submitted in accordance with the requirements of the University of Liverpool for the degree of Doctor in Philosophy by Sean Mather

Feb 2017

### Abstract

Up until 2007 the heart of the metal -oxide-semiconductor-field-effecttransistor (MOSFET) in computer processors was based on the Si-SiO<sub>2</sub>-poly Si system. This changed when Intel announced the fabrication of the high-k metal gate MOSFET. This was required because the SiO<sub>2</sub> layer had become too thin so that quantum mechanical tunnelling meant that the leakage current through the device was unacceptably high. As the high quality SiO<sub>2</sub> layer was the main reason for silicon it is now possible for a semiconductor with better electrical properties to be used. The International Technology Roadmap for Semiconductors (ITRS) states that this is due to happen in 2018. Germanium is one of the contending materials due to high carrier mobilities (2x electron and 4x hole enhancement over silicon).

This thesis studies the development of high-k dielectrics deposited by atomic layer deposition (ALD), specifically the dielectric constant enhancement of HfO<sub>2</sub> with the addition of titanium. Different preparation methods were then deployed to create Hafnium based gate stacks on germanium. These methodologies are divided into 4 sections. Firstly, to grow a germanium oxide layer by oxygen plasma with the subsequent deposition of high-k on top. Then Molecular Beam Epitaxy (MBE) of an ultra-thin aluminium layer to create an ultra-thin gate stack with high-k deposited on top to reduce the leakage current through the devices. Then ALD of a thin Al<sub>2</sub>O<sub>3</sub> layer with high-k on top

3

and finishes with sulphur passivation of the Ge interface with high-k on top. These material systems were characterised by both physical (ellipsometry, Xray diffraction, X-ray photoelectron spectroscopy, Transmission electron microscopy) and electrical (Capacitance-voltage, Current-voltage) means. The dielectric constant of HfO<sub>2</sub> was found to increase from 17 to 35 for the Ti<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub> system. This then reduced upon annealing to 27 with a 30 minute N<sub>2</sub> anneal at 500°C and 22 with a 30s spike anneal at 850°C.Growing a germanium oxide layer by oxygen plasma gave reasonable C-V characteristics but the thickness of the layer at 3nm was too large to make it suitable for extremely scaled devices

By giving the germanium a thermal clean in the MBE chamber and depositing an ultra-thin Aluminium layer which was subsequently oxidised a structure with an equivalent oxide thickness of 1.3nm were achieved with low leakage currents of 2x10<sup>-4</sup>Acm<sup>-2</sup> and low hysteresis of 10mV. The leakage current dropped to 3x10<sup>-7</sup>Acm<sup>-2</sup> for a sample with an EOT of 1.5nm. The equivalent oxide thickness (EOT) was found to be related to the temperature of the thermal preclean with higher temperatures giving lower EOT's due to a more efficient removal of the native oxide. EOT was also found to reduce for samples after a forming gas anneal which is attributed to densification of the layers and a reduction of the GeO<sub>x</sub> interfacial layer.

ALD of a thin  $AI_2O_3$  layer and subsequent plasma ALD of HfO<sub>2</sub> showed that significant regrowth of GeO<sub>x</sub> occurs even when 2nm thick  $AI_2O_3$  barrier is employed. The electrical data is similar to samples without the  $Al_2O_3$  layer which could be due to it not being thick enough to suppress an unwanted interfacial layer forming.

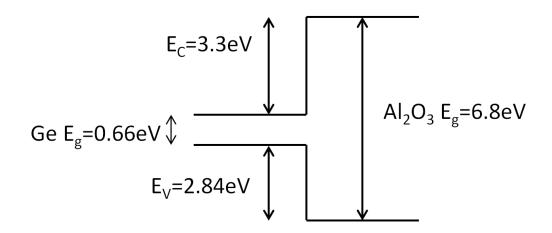

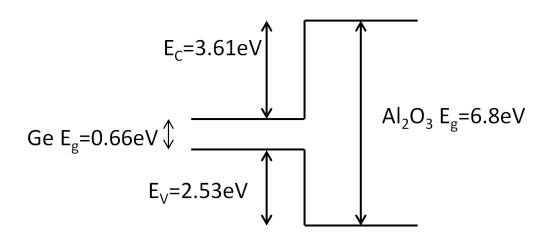

Sulphur passivation gave very good C-V data when Al<sub>2</sub>O<sub>3</sub> is used as a dielectric and conduction band offsets were calculated as being 3.3eV for S-passivated samples and 3.61eV without S-passivation. Both of these are well over the 1eV set out by the ITRS to reduce carrier injection from the channel through the device. Device performance was found to be not as good when HfO<sub>2</sub> was used as the dielectric as there is significant regrowth of the GeO<sub>x</sub> interfacial layer.

These studies show that there are a number of possible routes available for forming a gate stack on germanium and the control of the interface is the critical performance factor that needs to be controlled.

### **List of Publications**

- Mather. S, Sedghi. N, Althobaiti. M, Mitrovic. I. Z, Dhanak. V.R, Chalker.

P.R, Hall. S, *"Low EOT GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/ HfO<sub>2</sub> on Ge substrate using ultrathin Al deposition"*, (2013) Microelectronic Engineering, 109, pp. 126-128

- Werner. M, King. P.J, Hindley. S, Romani. S, Mather. S, Chalker. P.R, Williams. P.A, Van Den Berg. J.A, *"Atomic layer deposition of Ti- HfO<sub>2</sub> dielectrics"*, (2013) Journal of Vacuum Science and Technology A: Vacuum, Surfaces and films, 31 (1), art. no. 01A102

- Mitrovic. I. Z, Althobaiti. M, Weerakkody. A.D, Sedghi. N, Hall. S, Dhanak.

V.R, Mather. S, Chalker. P.R, Tsoutsou. D, Dimoulas. A, Henkel. C, Litta.

E.D, Hellstrom. P.E, Ostling. M, *"Interface engineering routes for a future CMOS Ge-based technology"* (2014) ECS Transactions, 61 (2), pp. 73-88

- Althobaiti. M, Mather. S, Sedghi. N, Dhanak. V.R, Mitrovic. I. Z, Hall. S, Chalker. P.R, *"Hafnia and alumina on sulphur passivated germanium"*, (2014) Vacuum, Article in Press, DOI: 10.1016/j.vacuum.2015.03.017

### Acknowledgements

For the chapter with Ti- HfO<sub>2</sub> growths on silicon the films were deposited by S. Mather/M. Werner/S. Hindley and P. J. King. TEM specimens were prepared by P. J. King and measurements performed by S. Romani. Heat treatments were performed by M. Werner and P. J. King. Electrical measurements were performed by S. Mather/M. Werner and P. J. King. XRD was performed by P. J. King. For the chapters on germanium MBE growths were performed by S. Mather and T. Joyce. TEM samples in Figure 44 and Figure 45 were measured by C. Dawson and S. Romani. XPS in Figure 42 and Figure 43 was performed by M. Althobaiti/ V. R. Dhanak and I. Z. Mitrovic. Some Al back contact and Au top contacts were deposited by N. Sedghi.

## Acronyms

| Symbol          | Name                             | Units                                           |

|-----------------|----------------------------------|-------------------------------------------------|

| ε <sub>0</sub>  | Permittivity of free space       | Fm <sup>-1</sup>                                |

| Φ               | Work function                    | eV                                              |

| ALD             | Atomic layer deposition          |                                                 |

| CVD             | Chemical vapour deposition       |                                                 |

| CET             | Capacitance equivalent thickness | nm                                              |

| D <sub>it</sub> | Density of interface states      |                                                 |

| EOT             | Equivalent oxide thickness       | nm                                              |

| E <sub>f</sub>  | Fermi level                      |                                                 |

| Ei              | Intrinsic Fermi level            |                                                 |

| Ec              | Conduction band                  |                                                 |

| Ev              | Valance band                     |                                                 |

| К               | Dielectric constant              |                                                 |

| Q               | Charge on an electron            | С                                               |

| μ               | Mobility                         | cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> |

| MBE             | Molecular beam epitaxy           |                                                 |

| TEM             | Transmission electron microscopy |                                                 |

| XPS             | X-ray photoelectron spectroscopy |                                                 |

| XRD             | X-ray diffraction                |                                                 |

## List of Figures

| Figure 1. Schematic of a pMOSFET device21                                                   |

|---------------------------------------------------------------------------------------------|

| Figure 2. nMOSFET with various gate voltages applied. The white circles                     |

| representing holes and the dark blue circles representing electrons22                       |

| Figure 3. EOT against year of production for bulk planer MOSFET devices [4].26              |

| Figure 4. Energy band diagram of a p-type MOS device under flat band                        |

| conditions where $E_{c}$ is the conduction band edge, $E_{i}$ is the intrinsic fermi level, |

| $E_F$ is the fermi level and $E_\nu$ is the valence band edge. The metal is on the left,    |

| the oxide in the middle and the semiconductor on the right27                                |

| Figure 5. Band Diagrams for a MOS device when in a) flat band b)                            |

| accumulation c) depletion and d) inversion29                                                |

| Figure 6. C-V characteristics of a MOS devices                                              |

| Figure 7. C-V graph showing the effect of fixed oxide charge32                              |

| Figure 8. Band diagram under flat band conditions where the crosses denote                  |

| the position of interface states                                                            |

| Figure 9. CV graph with the dotted line representing the stretch out effect due             |

| to interface states                                                                         |

| Figure 10. a) shows the system under flat band condition, b) shows Fowler-                  |

| Nordheim tunnelling and c) shows Frenkel-Poole tunnelling35                                 |

| Figure 11. Band gap against dielectric constant, from [7]40                                 |

| Figure 12. A schematic (left) of the gate stacks fabricated for TDS analysis. The                                          |

|----------------------------------------------------------------------------------------------------------------------------|

| results of the TDS are shown on the right, after Kita et al [12]43                                                         |

| Figure 13. XRD spectrum showing Ge $2p_{3/2}$ of DIW etched germanium (left) and                                           |

| UHV cleaned germanium (right) showing reduction in the germanium oxides                                                    |

| after TMA and water pulses. After Milojevic et al [14]44                                                                   |

| Figure 14. TEM image of a Ge/GeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> gate stack, after Zhang et al [15]45         |

| Figure 15. $D_{it}$ at -0.2eV as a function of GeO <sub>x</sub> thickness with the corresponding                           |

| D <sub>it</sub> distributions in the inset, after Zhang et al [16]46                                                       |

| Figure 16. Peak hole mobility as a function of EOT of the pMOSFETs fabricated                                              |

| in [17] compared with other work in the area, after Zhang et al [17]47                                                     |

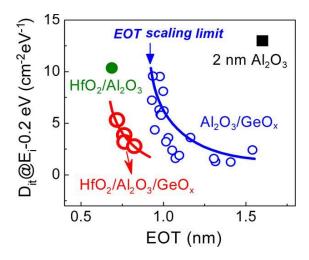

| Figure 17. $D_{it}$ as a function of EOT for gate stacks with and without using HfO <sub>2</sub>                           |

| for lowering the EOT, after [17]48                                                                                         |

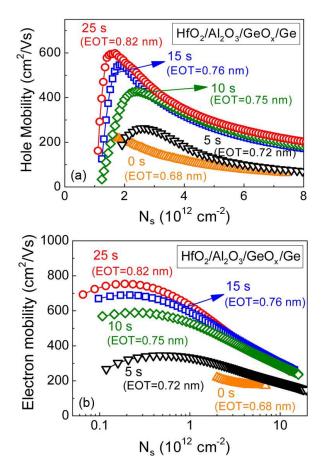

| Figure 18. Ge p and n-type MOSFETs giving the hole (a) and electron (b)                                                    |

| mobilities for Ge/GeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> gate stacks, after Zhang et al [17]48 |

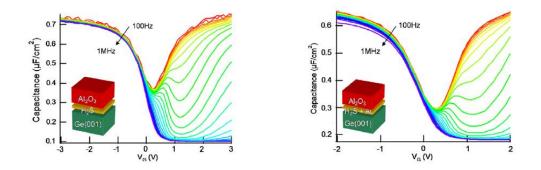

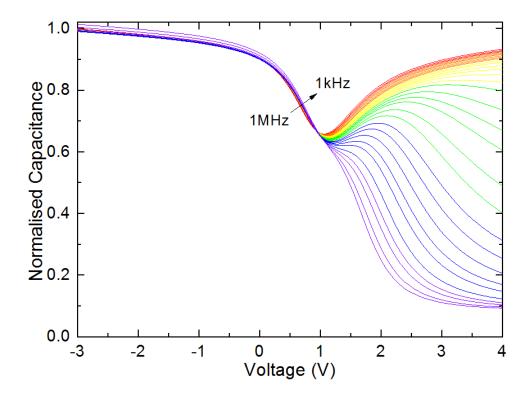

| Figure 19. CV characteristics as a function of frequency of $AI_2O_3/H_2S$ –Ge (left)                                      |

| and $Al_2O_3/Al/H_2S$ –Ge (right) MOS capacitors measured at RT, after Merckling                                           |

| et al [18]49                                                                                                               |

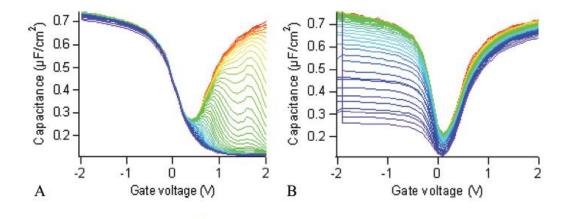

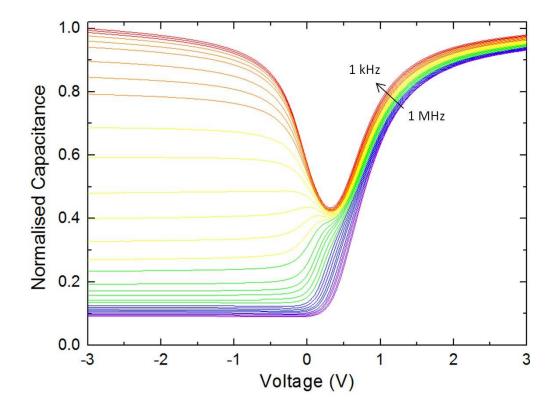

| Figure 20. CV as a function of frequency characteristics of Ge/S/Al <sub>2</sub> O <sub>3</sub> (8nm)                      |

| with p-type (left) and n-type (right) Ge, after Sioncke et al [19]50                                                       |

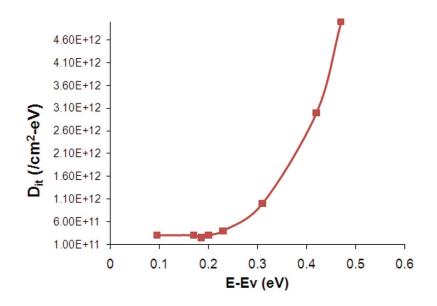

| Figure 21. D <sub>it</sub> distribution as a function of position in the band gap for a                                    |

| Ge/S/Al <sub>2</sub> O <sub>3</sub> (8nm) gate stack, after Sioncke et al [19]51                                           |

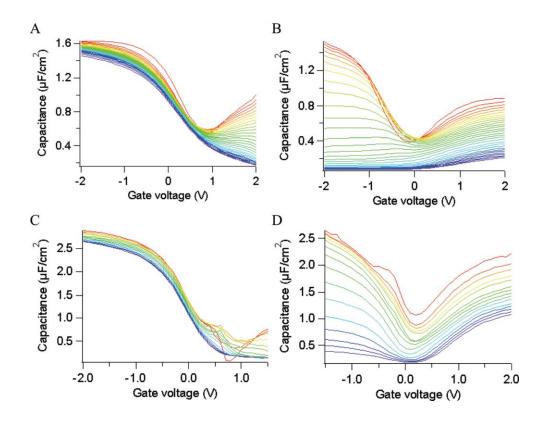

| Figure 22. CV as a function of frequency characteristics of Ge/S/ZrO <sub>2</sub> (8nm) on |

|--------------------------------------------------------------------------------------------|

| p-type (A) and n-type (B) Ge. Ge/S/HfO $_2$ (4nm) on p-type (C) and n-type (D) are         |

| also shown, after Sioncke et al [19]52                                                     |

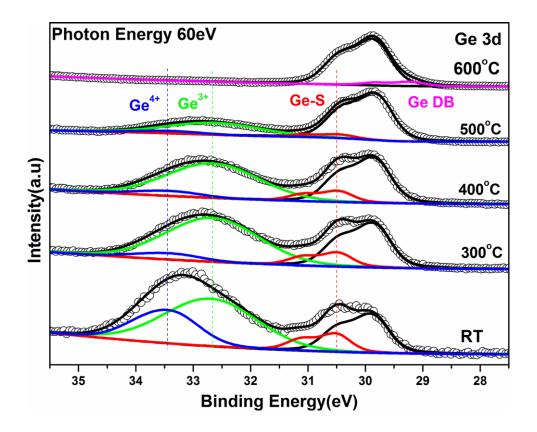

| Figure 23. XPS spectrum showing Ge 3d spectre of a Ge/S/Al $_2O_3$ sample after            |

| successive anneal cycles, after Challapan et al [20]53                                     |

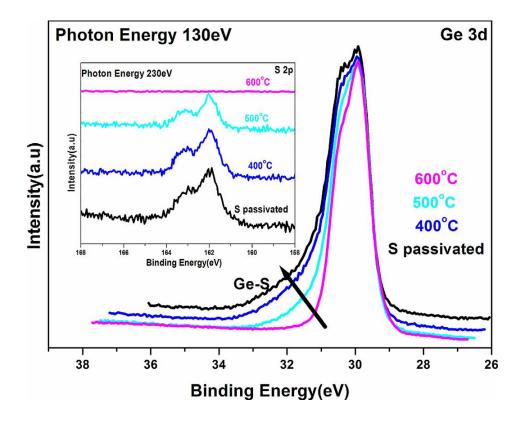

| Figure 24. XPS spectrum showing Ge 3d peak and S 2p peak (inset) for S-                    |

| passivated Ge at various temperatures, After Challappen et al [21]54                       |

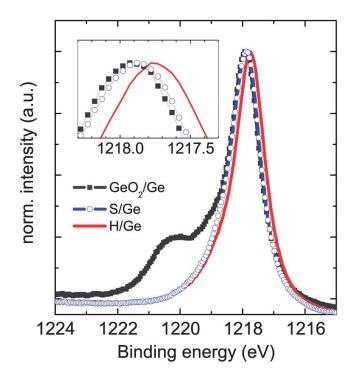

| Figure 25. XPS spectrum showing Ge $2p_{3/2}$ with HF cleaned Ge, S treated Ge             |

| and an untreated GeO $_2$ /Ge sample. The inset shows a close up of the                    |

| maximum intensity, After [22]55                                                            |

| Figure 26. The sequential nature of ALD schematic60                                        |

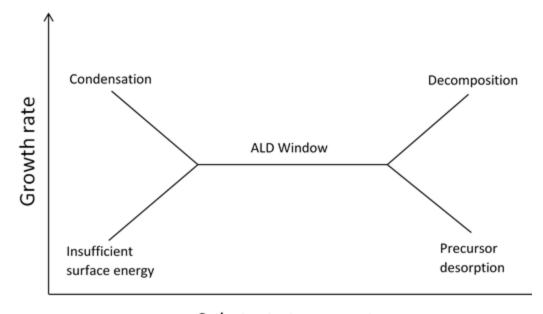

| Figure 27. ALD growth rate against substrate temperature62                                 |

| Figure 28. OpAL reactor schematic64                                                        |

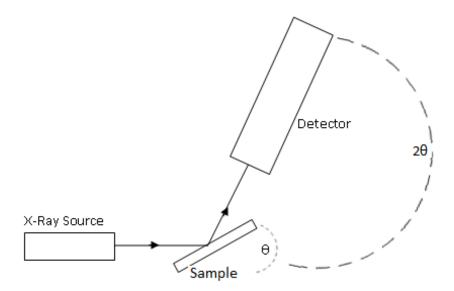

| Figure 29. The experimental set up for x-ray diffraction71                                 |

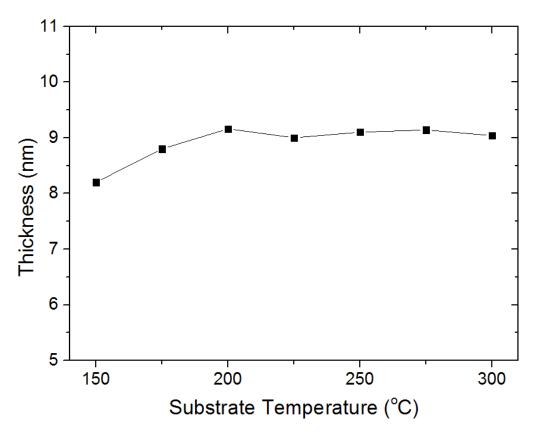

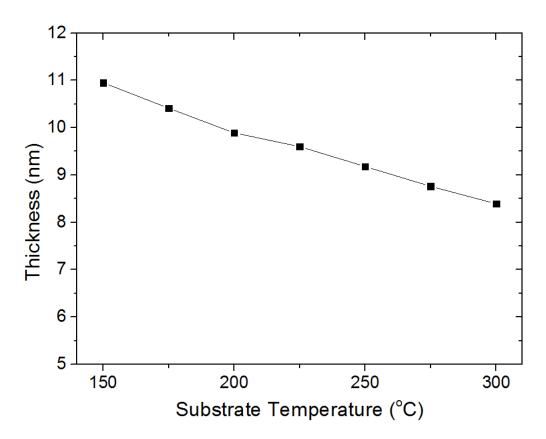

| Figure 30. The variation in $AI_2O_3$ thickness as a function of temperature75             |

| Figure 31. The variation in $AI_2O_3$ thickness as a function of temperature76             |

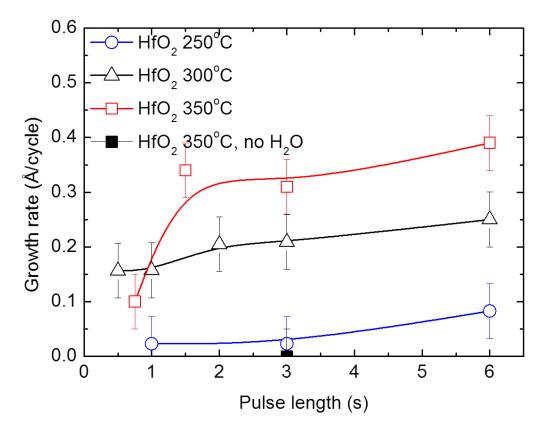

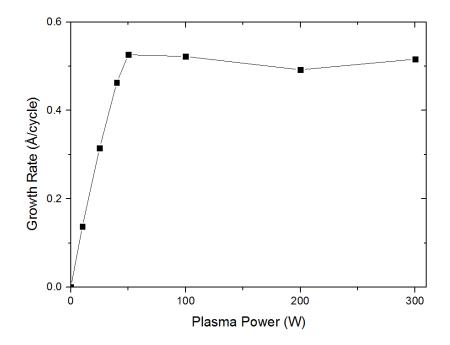

| Figure 32. Growth rate against pulse length for $HfO_2$ at different temperatures          |

|                                                                                            |

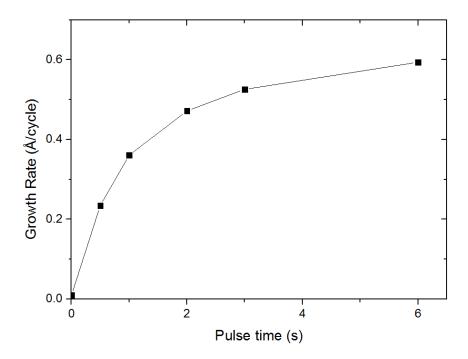

| Figure 33. Growth rate against oxygen plasma pulse time for $HfO_2$ deposited at           |

| 250°C79                                                                                    |

| Figure 34. Growth rate against oxygen plasma power for $HfO_2$ deposited at                |

| 250°C79                                                                                    |

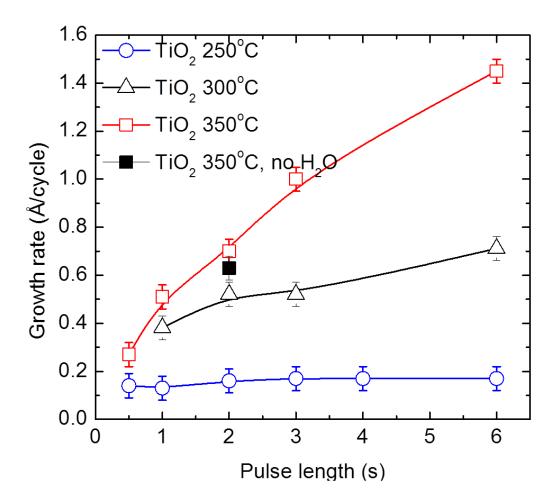

| Figure 35. Growth rate against pulse length for $TiO_2$ at different temperatures |  |

|-----------------------------------------------------------------------------------|--|

|                                                                                   |  |

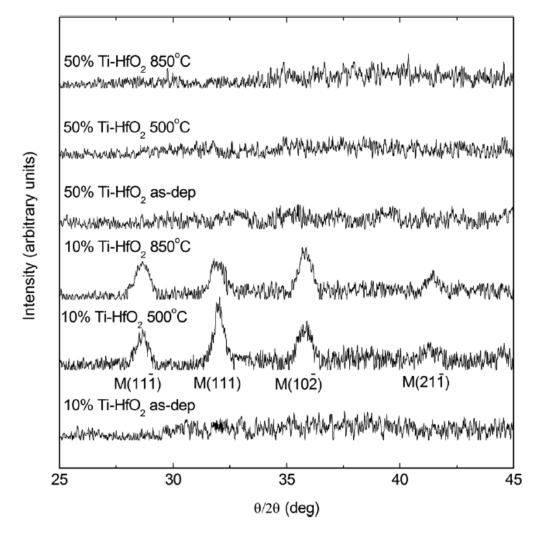

| Figure 36. XRD spectra showing the crystallisation of the 10% Ti doped film for   |  |

| both types of annealing in contrast to the 50% doped films remaining              |  |

| amorphous                                                                         |  |

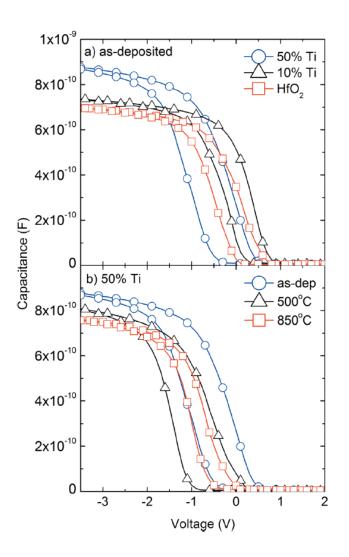

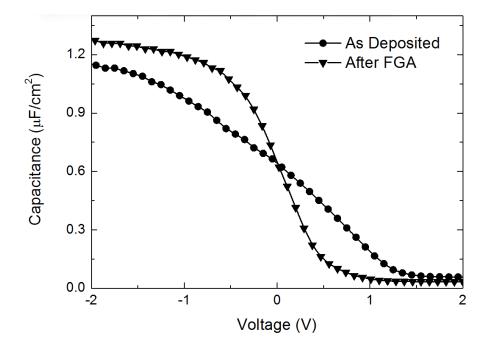

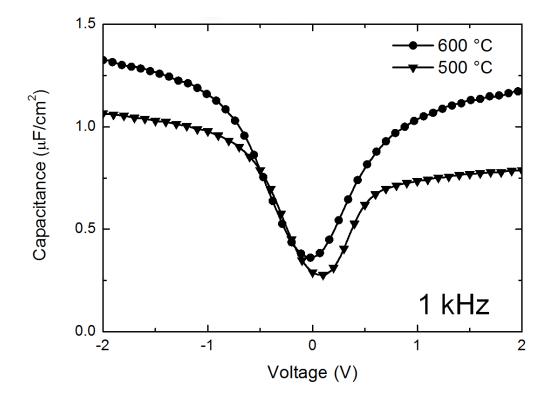

| Figure 37. C-V measurements showing the change in capacitance arising from        |  |

| the difference in dielectric constant and the reduction in this (as indicated by  |  |

| lower capacitance) when annealed84                                                |  |

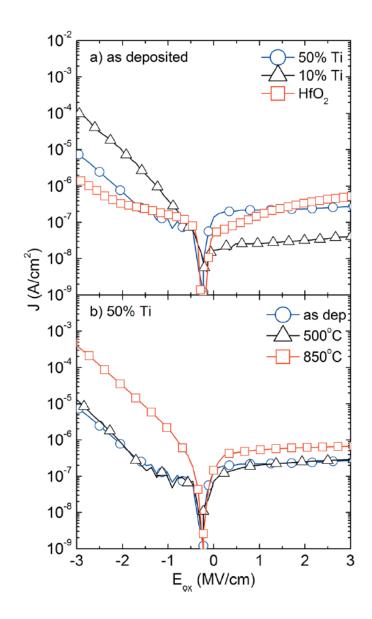

| Figure 38. IV leakage measurements for the Ti doped $HfO_2$ films85               |  |

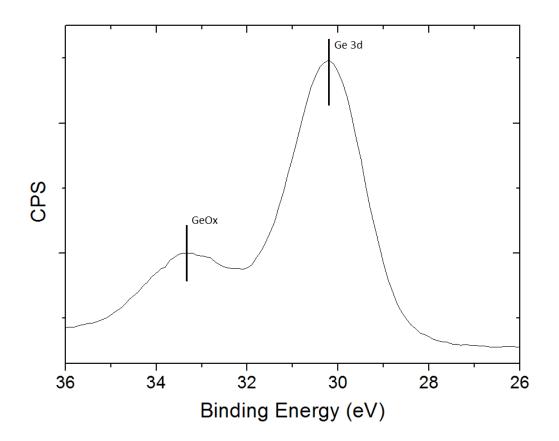

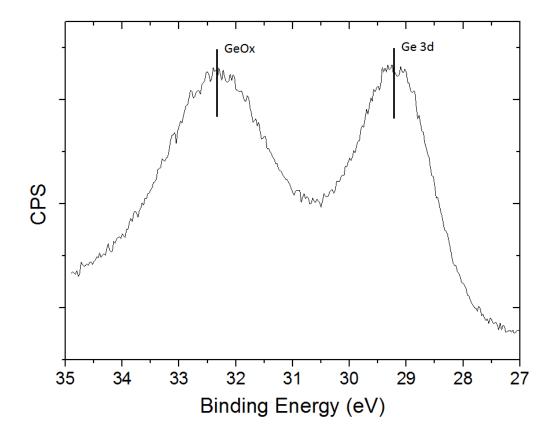

| Figure 39. XPS spectrum Ge 3d of plasma grown GeO <sub>x</sub> 89                 |  |

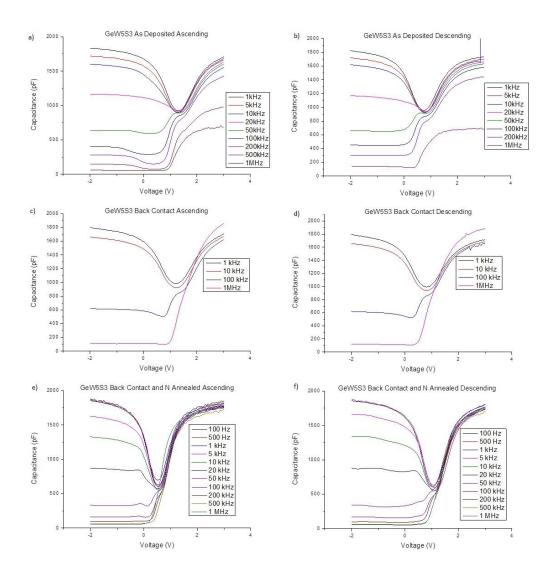

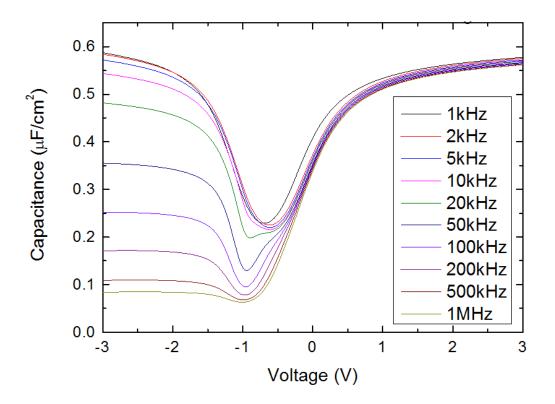

| Figure 40. CV as a function of frequency results on GeW5S3 with a) and b) as      |  |

| deposited, c) and d) with an Al back contact and e) and f) after a nitrogen       |  |

| anneal at 350°C for 30 minutes. Ascending indicates the voltage sweep going       |  |

| from negative to positive bias and descending indicates from positive to          |  |

| negative91                                                                        |  |

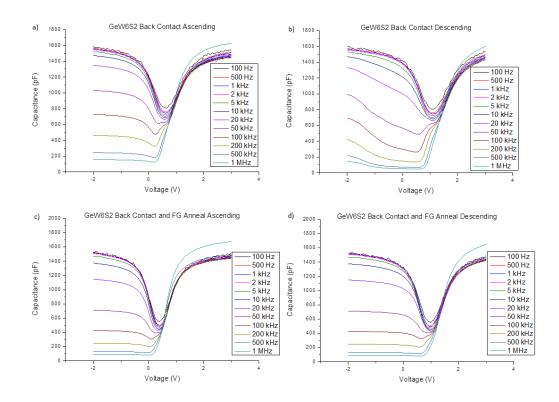

| Figure 41. CV as a function of frequency on GeW6S2 with a) and b) as              |  |

| deposited with Al back contact and c) and d) after a forming gas anneal at        |  |

| 350°C for 30 mins. Ascending indicates the voltage sweep going from negative      |  |

| to positive bias and descending indicates from positive to negative92             |  |

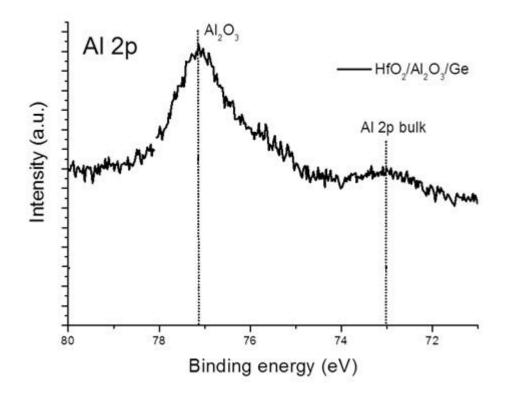

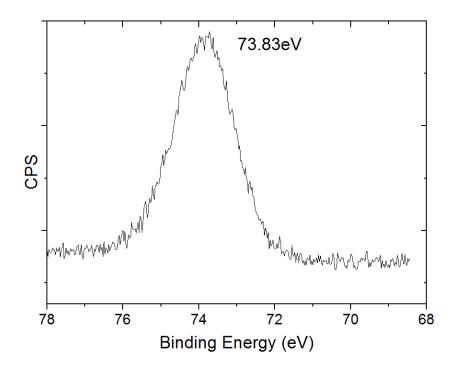

| Figure 42. XPS spectrum showing the results centred around Al 2p95                |  |

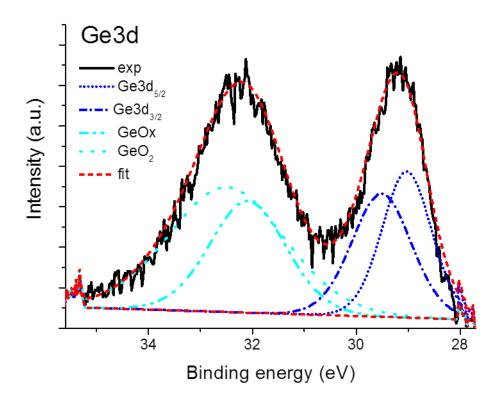

| Figure 43. XPS spectrum results centred around Ge 3d96                            |  |

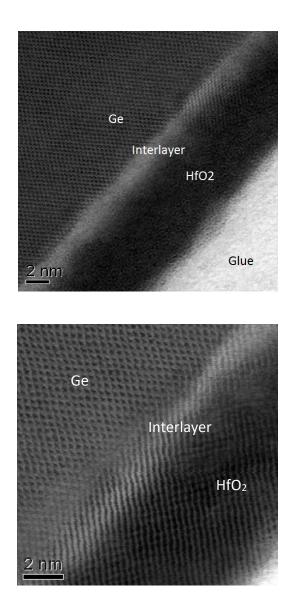

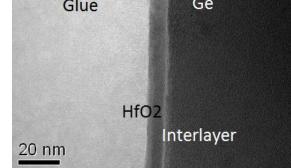

| Figure 44. TEM images under x6000k (top) and x10000k magnification               |

|----------------------------------------------------------------------------------|

| (bottom) in bright field mode97                                                  |

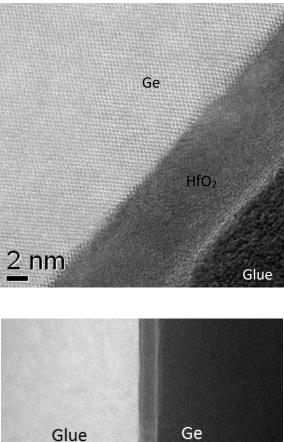

| Figure 45. TEM images under x5000k (top) and x1000k (bottom) magnification       |

| in dark field mode98                                                             |

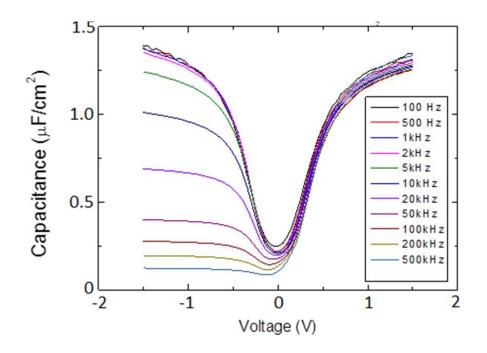

| Figure 46. Typical CV as a function of frequency scan for sample with 5s Al flux |

| and 3.5nm HfO <sub>2</sub> 101                                                   |

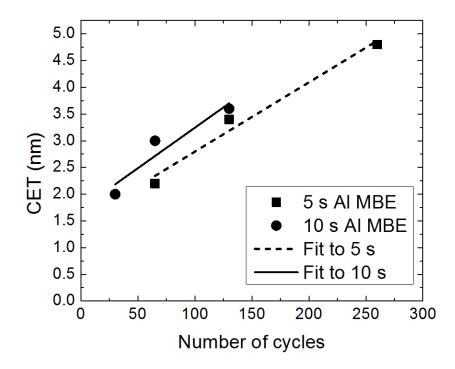

| Figure 47. CET against number of ALD cycles for 10s and 5s Al flux times 101     |

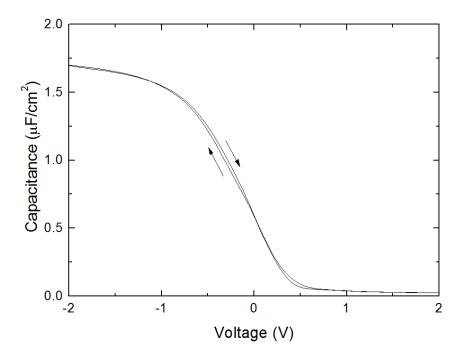

| Figure 48. CV data showing the hysteresis of sample with an EOT of 1.7nm         |

| measured at 1MHz 103                                                             |

| Figure 49. CV data showing an example of the effect of forming gas anneal on     |

| the C-V characteristics where the stretched out CV for the as deposited sample   |

| indicates a higher D <sub>it</sub> 103                                           |

| Figure 50. CV data showing the effect of the thermal preclean temperature on     |

| the EOT (shown by the increase in the capacitance) of samples with 7nm $HfO_2$   |

| on p-type germanium 104                                                          |

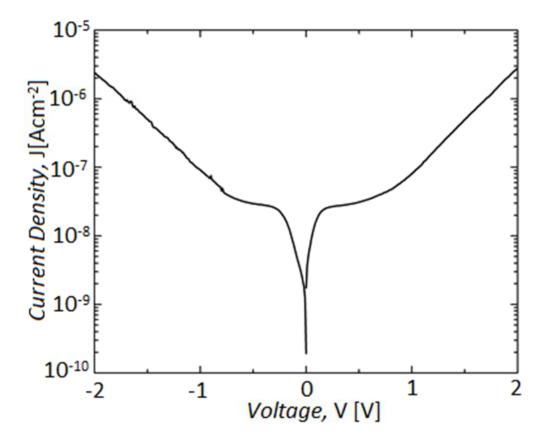

| Figure 51. Current density measurements for sample with 5s Al flux and 3.5nm     |

| HfO <sub>2</sub> 105                                                             |

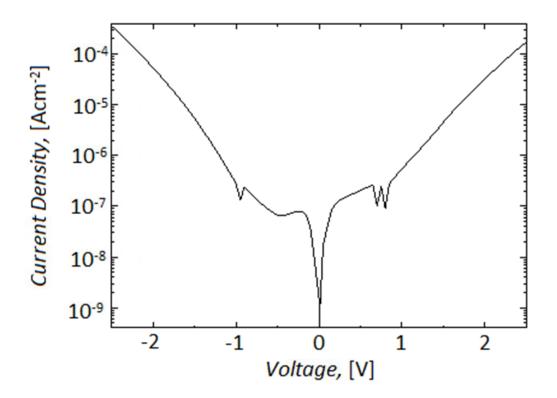

| Figure 52. Current density for sample cleaned at 600°C, 15s Al flux and 3.5nm    |

| $HfO_2$ with an EOT of 1.5nm                                                     |

| Figure 53. XPS spectrum of Ge 3d when $2nm$ of $Al_2O_3$ is grown thermally      |

| followed by 2nm HfO <sub>2</sub> grown using oxygen plasma 110                   |

| Figure 54. C-V as a function of frequency of 20nm $HfO_2$ grown using a plasma         |  |

|----------------------------------------------------------------------------------------|--|

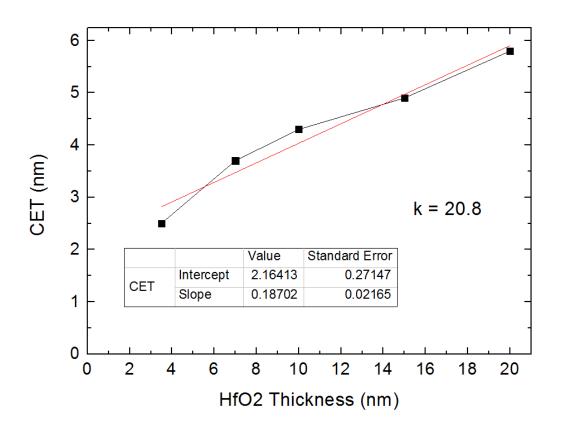

| process on n-type Ge 111                                                               |  |

| Figure 55. CET against $HfO_2$ thickness with a line of best fit indicating the y-axis |  |

| intercept and the slope of the graph 112                                               |  |

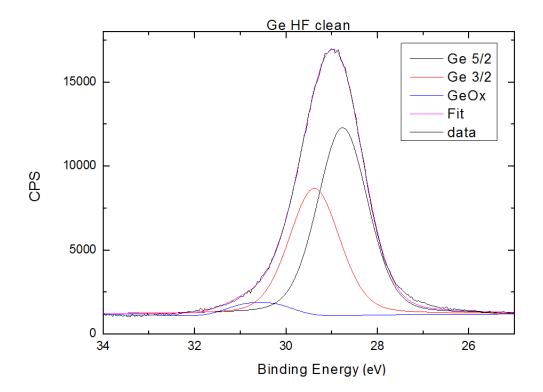

| Figure 56. XPS spectrum of HF cleaned Ge3d115                                          |  |

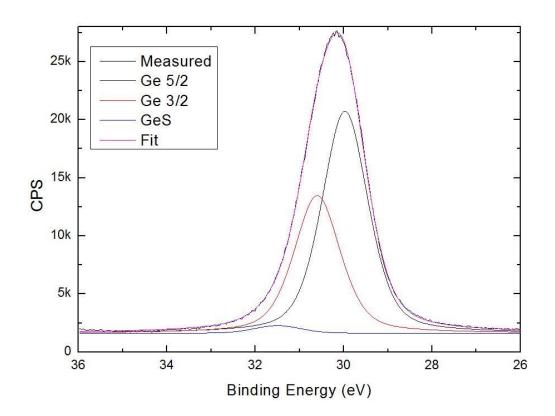

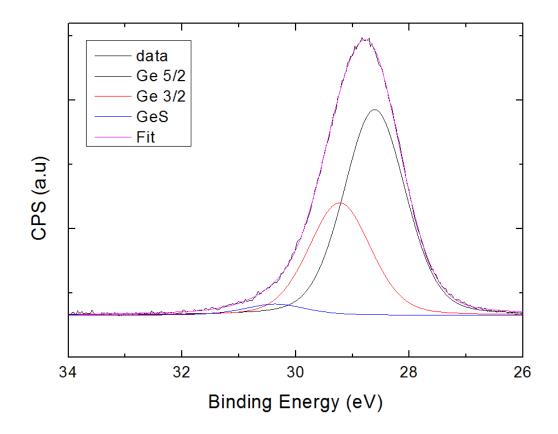

| Figure 57. XPS spectrum of S-passivated Ge3d 116                                       |  |

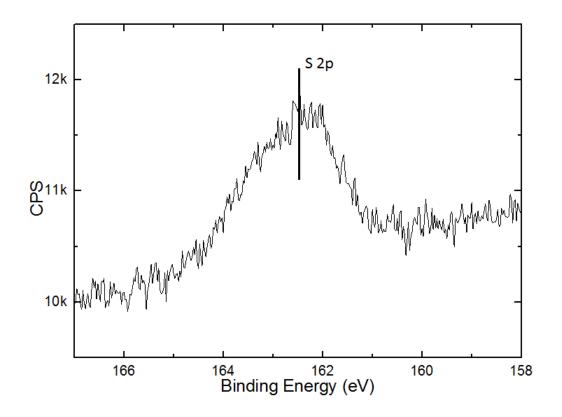

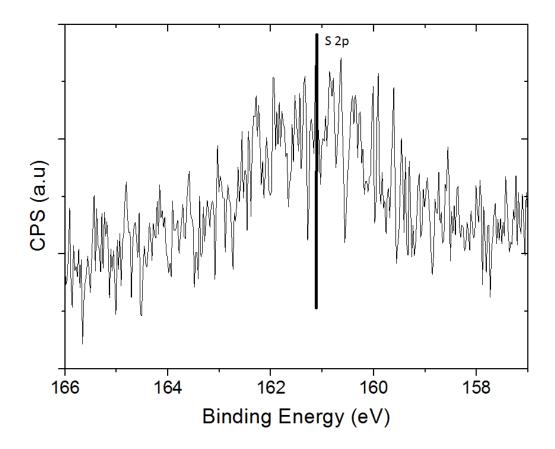

| Figure 58. XPS spectrum of S-passivated S 2p 117                                       |  |

| Figure 59. XPS spectrum S-passivated Ge3d with 2nm Al $_2O_3$ deposited                |  |

| thermally showing the presence of a GeS peak at higher binding energy than             |  |

| the main Ge3d peak 119                                                                 |  |

| Figure 60. XPS spectrum of S-passivated S 2p with 2nm $Al_2O_3$ 120                    |  |

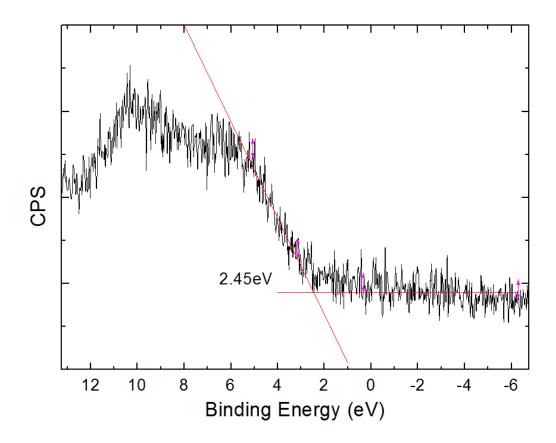

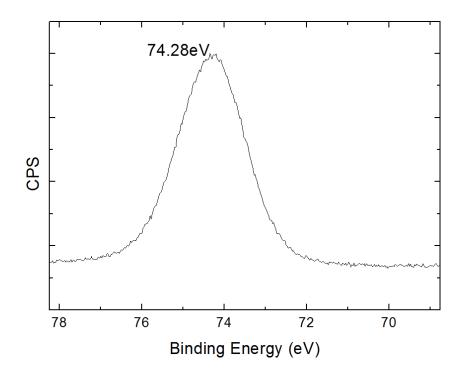

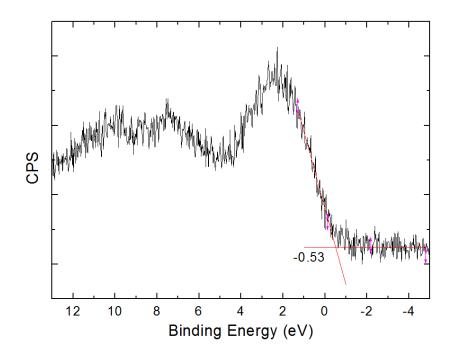

| Figure 61. XPS spectrum of valence band maximum of thick $AI_2O_3$ sample 121          |  |

| Figure 62. XPS spectrum of Al 2p of thick $Al_2O_3$ sample 122                         |  |

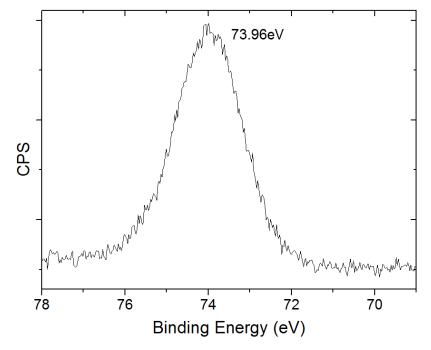

| Figure 63. XPS spectrum of Al 2p of S-passivated Ge with 2nm Al $_2O_3$ cap 122        |  |

| Figure 64. Band schematic of S-passivated Ge with $AI_2O_3$                            |  |

| Figure 65. XPS spectrum of valence band maximum of a cleaned Ge sample 124             |  |

| Figure 66. XPS spectrum of Al 2p of HF cleaned Ge with thin Al $_2O_3$ cap 124         |  |

| Figure 67. Band schematic of HF cleaned Ge with $AI_2O_3$                              |  |

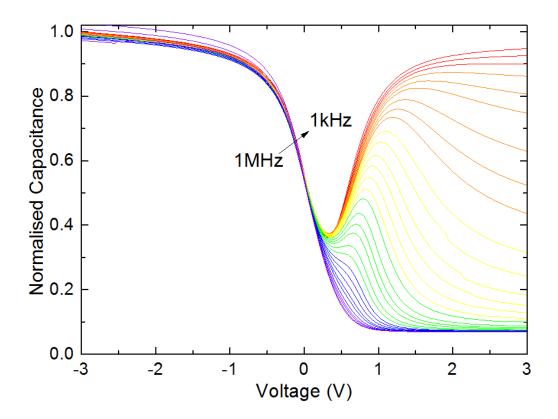

| Figure 68. CV as a function of frequency of $AI_2O_3$ on p-type S-passivated Ge 126    |  |

| Figure 69. CV as a function of frequency of $Al_2O_3$ on p-type Germanium 127          |  |

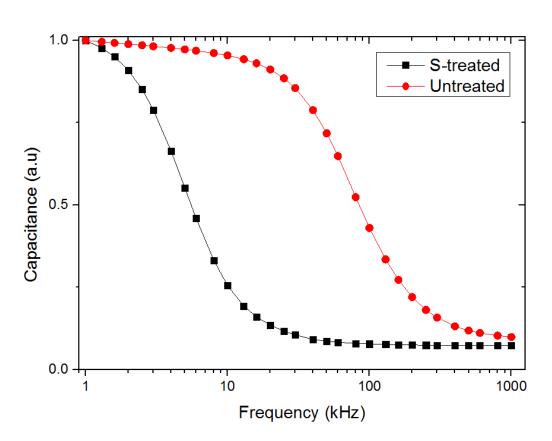

| Figure 70. Inversion Capacitance against frequency for p-type Ge with $AI_2O_3$        |  |

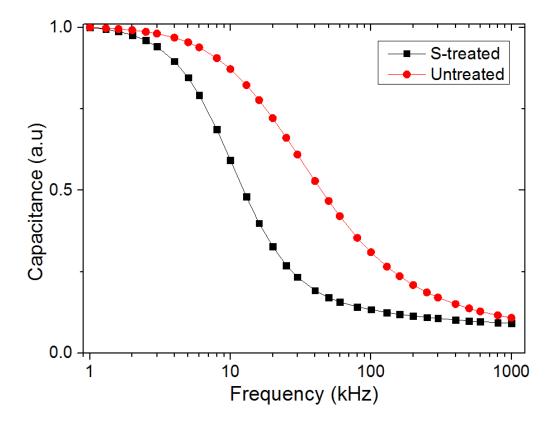

| with and without S-passivation128                                                      |  |

| Figure 71. CV as a function of frequency of $AI_2O_3$ on n-type S-passivated Ge 129 |

|-------------------------------------------------------------------------------------|

| Figure 72. CV as a function of frequency of $AI_2O_3$ on p-type Germanium 130       |

| Figure 73. Inversion Capacitance against frequency for n-type Ge with $Al_2O_3$     |

| with and without S-passivation 131                                                  |

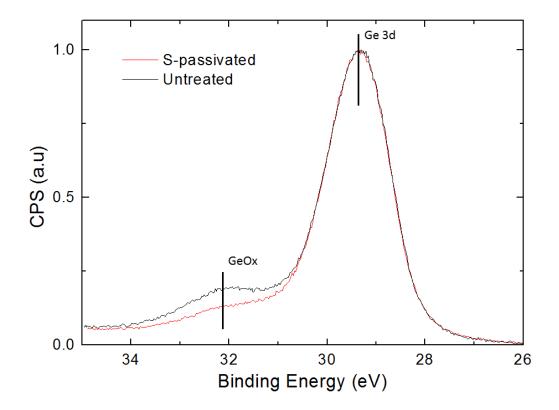

| Figure 74. XPS spectrum showing Ge3d of thermal $HfO_2$ grown with and              |

| without S-passivation. S-passivated trace has been shifted by 0.16eV to             |

| coincide with untreated sample for clarity 133                                      |

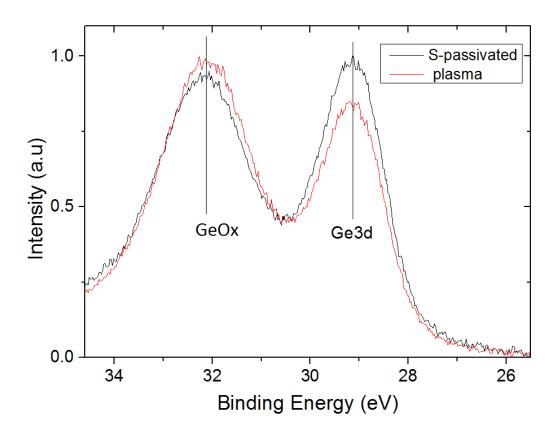

| Figure 75. XPS spectrum of Ge3d of plasma $HfO_2$ grown with and without S-         |

| passivation 134                                                                     |

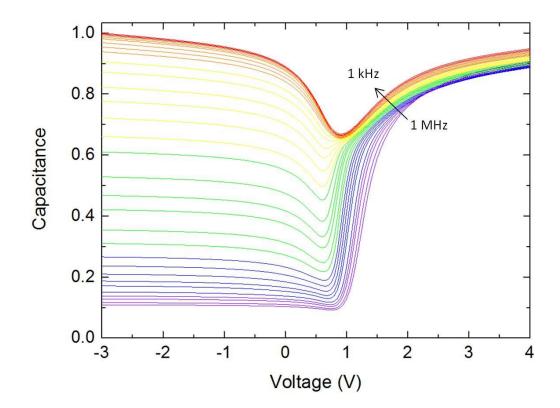

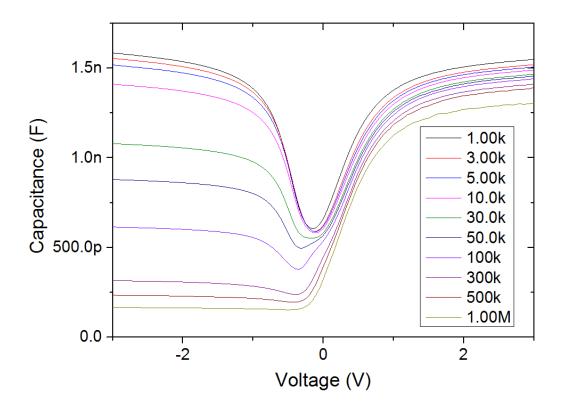

| Figure 76. CV data as a function of frequency for S-passivated Ge with 13nm of      |

| HfO <sub>2</sub> 135                                                                |

## Table of Contents

| Abstract                                   | 3  |

|--------------------------------------------|----|

| 1. Introduction                            | 19 |

| 1.1 Outline of Thesis                      | 19 |

| 1.2 Technological Context                  | 20 |

| 1.2.1 MOSFET origins and evolution         | 20 |

| 1.2.2 Scaling                              | 23 |

| 1.2.3 MOS Capacitor physics                | 26 |

| 1.2.4 Current Density-Voltage              | 34 |

| 1.3 High-k dielectrics                     | 37 |

| 1.3.1 Dielectric theory                    | 37 |

| 1.3.2 Choice of High-k                     | 38 |

| 1.4 High Mobility MOSFET Channels          | 39 |

| 1.4.1 Why are they Necessary?              |    |

| 1.4.2 Channel Materials                    | 41 |

| 1.5 Literature Review                      | 42 |

| 2. Growth and Processing                   | 57 |

| 2.1 Germanium Substrate Cleaning           | 57 |

| 2.2 Atomic Layer Deposition                | 58 |

| 2.2.1 The ALD Process                      | 58 |

| 2.2.2 The Opal Reactor                     | 64 |

| 2.2.3 Thermal Deposition of Oxides         | 64 |

| 2.2.4 Plasma Enhanced Deposition of Oxides | 65 |

| 2.3 Molecular Beam Epitaxy                 | 65 |

| 2.4 Metal Gate and Back Contact Deposition | 66 |

| 2.5 Physical Characterisation              | 66 |

| 2.5.1 Ellipsometry                         | 66 |

| 2.5.2 XPS                                  | 68 |

| 2.5.3 XRD                                  | 69 |

| 2.5.4 TEM                                  | 71 |

| 2.6 Electrical Characterisation            | 72 |

| 2.6.1 Capacitance-Voltage                  | 72 |

| 2.6.2 Current Voltage                      | 73 |

| 3. Growth of $Al_2O_3$ and (Ti-doped) HfO <sub>2</sub> on Silicon                       | 74      |

|-----------------------------------------------------------------------------------------|---------|

| 3.1 Al <sub>2</sub> O <sub>3</sub> Growth on Silicon                                    | 74      |

| 3.1.1 Thermal Growth Of Al <sub>2</sub> O <sub>3</sub>                                  | 74      |

| 3.1.2 Plasma Growth of $Al_2O_3$                                                        | 75      |

| 3.2 HfO <sub>2</sub> Growth on Silicon                                                  | 77      |

| 3.2.1 Thermal growth of HfO <sub>2</sub>                                                | 77      |

| 3.2.2 Plasma enhanced growth of HfO <sub>2</sub>                                        | 78      |

| 3.3 Ti-doped HfO <sub>2</sub>                                                           | 80      |

| 3.3.1 Growth Characterisation                                                           | 80      |

| 3.3.2 XRD of (Ti-doped) HfO <sub>2</sub>                                                | 82      |

| 3.3.3 Electrical Characterisation                                                       | 83      |

| 3.4 Chapter Summary                                                                     | 85      |

| 4. Plasma grown GeO <sub>x</sub> with $HfO_2$ cap                                       | 87      |

| 4.1 Growth                                                                              | 87      |

| 4.2 XPS of Plasma grown GeO <sub>x</sub>                                                | 89      |

| 4.3 Electrical Characterisation of plasma grown GeO <sub>x</sub> /HfO <sub>2</sub> Gate | Stack90 |

| 4.4 Chapter Summary                                                                     | 93      |

| 5. MBE of thin Al with $HfO_2$ cap                                                      | 94      |

| 5.1 Growth Conditions                                                                   | 94      |

| 5.2 XPS of Ge/GeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub>        | 95      |

| 5.3 TEM                                                                                 | 97      |

| 5.4 Electrical Characterisation                                                         | 99      |

| 5.4.1 CV Characteristics                                                                | 99      |

| 5.4.2 I-V Characterisation                                                              | 105     |

| 5.5 Chapter Summary                                                                     | 106     |

| 6. ALD of Thin $Al_2O_3$ with $HfO_2$ Cap                                               | 109     |

| 6.1 Growth                                                                              | 109     |

| 6.2 XPS Characterisation                                                                | 109     |

| 6.3 Electrical Characterisation                                                         | 110     |

| 6.4 Chapter Summary                                                                     | 112     |

| 7. Sulphur Passivation of Germanium                                                     | 114     |

| 7.1 Growth Conditions                                                                   | 114     |

| 7.2 XPS of (S-passivated) Germanium                                                     | 115     |

| 7.3 $AI_2O_3$ on (S-passivated) Germanium | 118 |

|-------------------------------------------|-----|

| 7.3.1 XPS Characterisation                | 118 |

| 7.3.2 Electrical Characterisation         | 126 |

| 7.4 $HfO_2$ on (S-passivated) Germanium   | 132 |

| 7.4.1 XPS Characterisation                | 132 |

| 7.4.2 Electrical Characterisation         | 134 |

| 7.5 Chapter Summary                       | 136 |

| 8.1 Main Conclusions                      | 139 |

| 8.2 Prospects of Future work              | 140 |

#### <u>1. Introduction</u>

#### 1.1 Outline of Thesis

Chapter 1 outlines the technological context for the research presented. This includes MOSFET operation and MOS physics, the rationale for the inclusion of high k dielectrics and high mobility channels and a literature review. Chapter 2 outlines the experimental techniques employed in the fabrication and characterisation of the gate stacks. Chapter 3 presents research into the deposition of high k dielectrics on silicon by ALD. This includes  $Al_2O_3$ , HfO<sub>2</sub> and Ti-doped  $HfO_2$ . Chapter 4 presents work on germanium with oxygen plasma grown GeO<sub>x</sub> layer with an ALD grown HfO<sub>2</sub> cap. Chapter 5 presents work where an ultrathin MBE deposited layer of Al (oxidised to Al<sub>2</sub>O<sub>3</sub>) with the subsequent deposition of high k by ALD to scale the EOT of MOS devices down. Chapter 6 has similar device structures as chapter 5 but this time with the Al<sub>2</sub>O<sub>3</sub> layer deposited by ALD. Chapter 7 presents work where the surface of germanium is passivated by sulphur deposition (via a  $(NH_4)_2S$  dip) with high k deposited by ALD on top. Chapter 8 has the conclusion and prospects for future work.

#### 1.2 Technological Context

#### 1.2.1 MOSFET origins and evolution

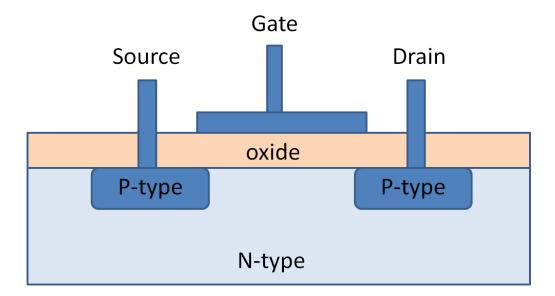

The metal-oxide-semiconductor-field-effect-transistor (MOSFET) is one of the most important inventions there has ever been. It has enabled the modern computer age which has meant advances in all realms of science and technology. The first transistor (which was a point contact transistor) was made from germanium at Bell laboratories by Shockley, Bardeen and Brattain in 1947 [1]. It was not until a decade later that an integrated circuit (IC), also on germanium, was developed by Kilby at Texas Instruments with silicon IC's following soon after. These early ICs were based on junction transistors and these presented many problems with the junction surfaces which caused significant reliability issues. In 1958 Attala of Bell Laboratories presented work [2] on thermally oxidised silicon and suggested the MOSFET device to make use of this work. Figure 1 shows a schematic of a pMOSFET device.

A semiconductor has the important property that the conductivity of the material can be modified by the addition of dopant atoms in the semiconductor crystal. An undoped semiconductor has an equal number of electron and holes that are created by thermal excitation or by defects in the crystal lattice. If some of the atoms are substituted by a different element, then an imbalance in the number of charge carriers forming a semiconductor with an excess of electrons or holes.

20

Figure 1. Schematic of a pMOSFET device

An example of this is that if a group IV semiconductor, e.g. Ge, is doped with a group IV element such as Sb. These Sb atoms substitute Ge in the crystal and as Sb has a higher number of valance electrons this means that for every dopant atom there is an extra electron in the lattice that contributes to macroscopic charge transport. This material would then be deemed to be n-type. The analogous argument holds true for if a group III atom is substituted into the lattice then there will be an excess of holes and this is a p-type semiconductor. The doping levels are typically of the order of a few millionths of a percent.

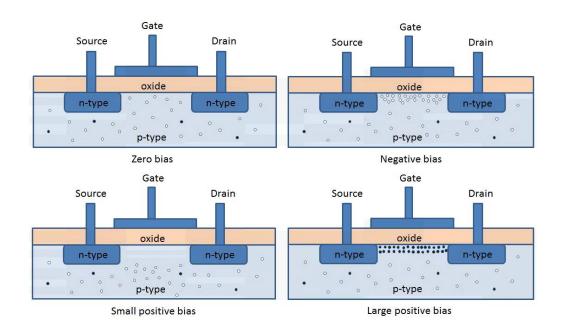

The basic principle of a MOSFET is that when a voltage is applied to the gate the conductivity of the channel is changed. How this conductivity varies with gate voltage is described in more detail on page 26 but for a description of how a MOSFET works this detail is not necessary. Figure 2 shows a schematic of what is happening to the charge carriers under the gate electrode for different gate biases for an n-type MOSFET.

Figure 2. nMOSFET with various gate voltages applied. The white circles representing holes and the dark blue circles representing electrons

When there is no bias applied to the gate in a nMOSFET there is no conduction possible from the source to the drain but as the bias is made more positive the conductivity of the channel changes until the majority charge carrier in the semiconductor under the gate changes to become negative. This then forms a conductive channel from the source to the drain. Gordon Moore made a famous prediction in 1965 that the number of transistors on a chip would double every two years[3]. This prediction became the driving force in improving the manufacturing processes and then became known as Moore's Law. This led to improving the performance of devices by scaling the device dimensions down using constantly developing new fabrication methods. The MOSFET device stayed broadly the same but smaller. For the continued scaling set by Moore's law to continue something had to change as the physical limit of the some of the device materials were being reached. For the area of the gate electrode, A, to be made smaller and for the capacitance, *C*, to remain the same then according to equation 1 the thickness of the insulating layer, t, must be made smaller or the insulating layer be replaced with a different material with a higher dielectric constant, k as  $\varepsilon_0$  is the permittivity of free space and is a constant and therefore cannot be changed.

$$C = \frac{k\varepsilon_0 A}{t}$$

Eq. 1

As the thickness for  $SiO_2$  is scaled further it becomes possible for electrons to quantum mechanically tunnel directly from the gate to the semiconductor which is known as leakage current. To reduce these high leakage currents the only option is to replace the  $SiO_2$  layer with a layer with a higher  $\kappa$  and have this layer thicker to reduce the leakage current. The dielectric constant of  $SiO_2$ is 3.9 so this means that if a dielectric had a  $\kappa$  ten times greater than  $SiO_2$  then the thickness of the dielectric can be ten times larger and still have the same capacitance. The equivalent oxide thickness (EOT) is a measure of how thick a layer of  $SiO_2$  would have to be to get the same capacitance as a high  $\kappa$ dielectric and is given by

$$EOT = t_{high k} \left( \frac{k_{SiO_2}}{k_{high k}} \right)$$

Eq. 2

Where  $t_{highk}$  is the thickness of the high k layer,  $k_{SiO_2}$  and  $k_{highk}$  are the dielectric constants of the SiO<sub>2</sub> and the high k layer respectively.

The EOT of a gate stack is not directly measurable from the C-V data. This is due to a contribution to the capacitance from the semiconductor ( $C_{channel}$ ) and the gate metal ( $C_{metal}$ ) as the accumulation layer cannot exist infinitely close to the interfaces. Equation 3 shows how the total gate stack capacitance (C) is modelled.

$$\frac{1}{c} = \frac{1}{C_{ox}} + \frac{1}{C_{metal}} + \frac{1}{C_{channel}}$$

Eq.3

This means that the measured capacitance has contributions from the semiconductor and metal as shown in equation 4 where the capacitance equivalent thickness (CET) is the measured value.

$$CET = EOT + t_{metal} + t_{channel}$$

Eq.4

These electrical thickness contributions from the metal and the channel are intrinsic to the material and the contribution is taken to be 0.3nm so when an EOT value in this thesis is presented it is calculated according to equation 5.

$$EOT = CET - 0.3nm$$

Eq.5

By modelling the device structure as two capacitors in series as shown by

$$\frac{1}{C} = \frac{1}{C_{HK}} + \frac{1}{C_{IL}}$$

Eq.6

where C is the measured capacitance,  $C_{HK}$  is the capacitance of the high k layer and  $C_{IL}$  is the capacitance of the interfacial layer. From this the dielectric constant of the film can be calculated from equation 7

$$k_{HK} = \frac{t_{HK}k_{IL}}{CET - t_{IL}}$$

Eq.7

where  $t_{HK}$  is the thickness of the high k layer,  $k_{IL}$  is the dielectric constant of the interfacial layer and  $t_{IL}$  is the thickness of the interfacial layer.

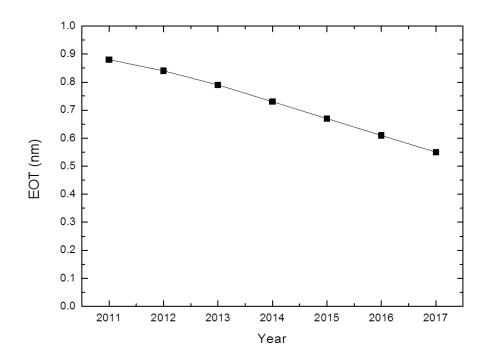

For application in MOS technologies this EOT needs to be less than 1nm according to the International Technology Roadmap for Semiconductors (ITRS) and the requirements from the 2013 ITRS report is shown in Figure 3.

*Figure 3. EOT against year of production for bulk planer MOSFET devices* [4]

#### 1.2.3 MOS Capacitor physics

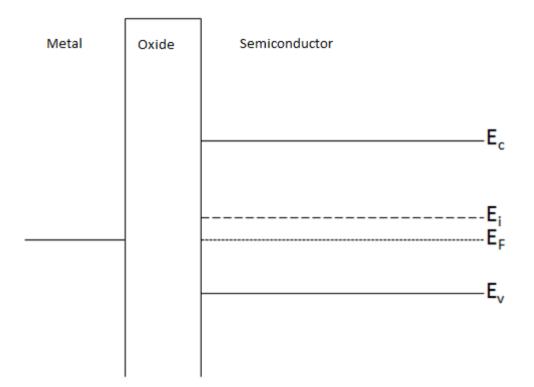

The heart of the MOSFET is the MOS capacitor. This is a very useful device in research and development as many of the MOSFET characteristics can be optimised first by fabricating the MOS capacitor. This approach is advantageous as the MOS capacitor is much quicker and simpler to fabricate. Figure 4 shows a typical band diagram of a MOS device.

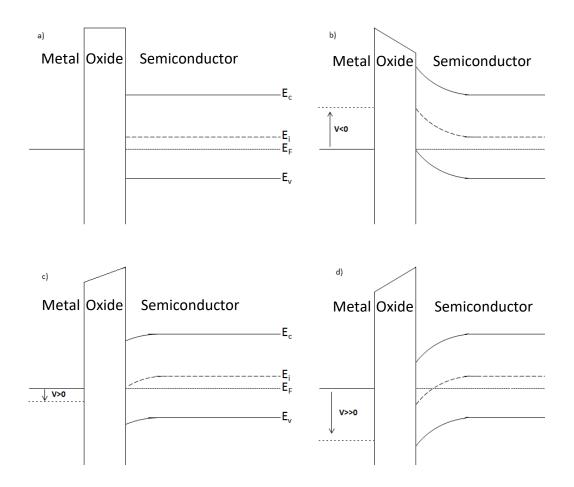

Figure 4. Energy band diagram of a p-type MOS device under flat band conditions where  $E_c$  is the conduction band edge,  $E_i$  is the intrinsic fermi level,  $E_F$  is the fermi level and  $E_v$  is the valence band edge. The metal is on the left, the oxide in the middle and the semiconductor on the right

The density of charge carriers (electrons and holes) at the semiconductordielectric interface varies as a function of applied gate voltage. This is the most important aspect of how the capacitance in a MOS capacitor changes with the given potential. The carrier density is related to the difference in the Fermi level ( $E_F$ ) and the intrinsic Fermi level ( $E_i$ ) and for a p-type semiconductor the concentration of holes is given by

$$p_p = n_i e^{\frac{(E_i - E_F)}{kT}}$$

Eq.8

Where  $p_p$  is the concentration of holes in a p-type semiconductor,  $n_i$  is the intrinsic carrier concentration, k is the Boltzmann's constant and T is the temperature.

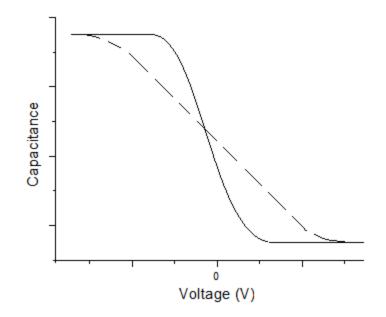

When a negative bias is applied to the metal gate the bands bend as shown in Figure 5b) and therefore  $E_i - E_F$  increases at the surface of the semiconductor and the dielectric which means that the concentration of holes increases as can be seen from equation [eq: carrier density] causing the semiconductor to be in accumulation and therefore the capacitance is at a maximum acting as a standard parallel plate capacitor. The physical process behind this is that the semiconductor already has an intrinsic positive charge and the application of a negative bias to the gate attracts further positive charge from the bulk of the semiconductor whilst also repelling the negative charge that is present when under flat band conditions. The capacitance is measured performing a DC sweep with an AC ripple on it. This accumulation capacitance should be the same across all the frequency range measured (0.1-1MHz) as the majority carriers (holes in this case) are able to respond almost immediately to the changing field.

28

Figure 5. Band Diagrams for a MOS device when in a) flat band b) accumulation c) depletion and d) inversion

When a small positive bias is applied to the gate (as in Figure 5c) the bands start to bend downwards and  $E_i - E_F \rightarrow 0$  so that  $p_p = n_i$ . As  $n_i^2 = p_p n_p$ where  $n_p$  is the electron concentration for a p-type semiconductor, it can be shown that there is no charge present at the surface as shown by

$$n_p = n_i e^{rac{(E_F - E_i)}{kT}}$$

Eq.9

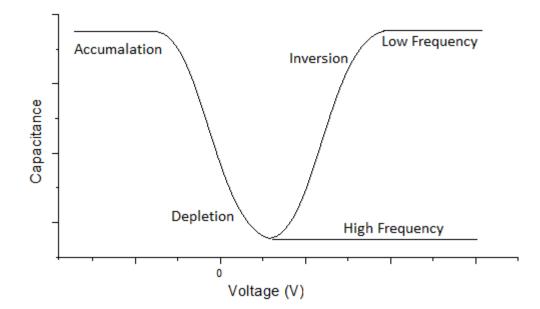

due to  $p_p = n_p$  causing the device to be in depletion and the capacitance to be at a minimum. If the positive bias is further increased (as in Figure 5d), the bands bend further so that  $E_i$  crosses  $E_F$  causing  $p_p$  to be less than  $n_i$  from equation [eq: carrier density]. This now means that  $n_p$  is larger than  $n_i$  ( $E_F$  –  $E_i > 0$ )so that  $n_p > p_p$  causing the device to be in inversion. To explain this from a physical perspective means considering how the minority and majority carriers respond to the applied field from the positive gate bias. If a larger positive bias is applied to the gate, then this will cause the majority carriers (holes) to be repelled from the interface and for the minority carriers (electrons) to be attracted to the interface. These electrons then form a small inversion layer at the interface where they now become the majority carriers. This now acts again like a parallel plate capacitor and the capacitance should be the same as in the accumulation case and this inversion layer is the channel layer in a transistor for switching the transistor on and off. If the frequency is too large then the minority carriers do not have enough time to react to the changing bias and are repelled from the interface and an inversion layer cannot form, when this happens the device goes into depletion. Since there is now no charge present at the interface the capacitance is very low. For even higher frequencies the width of the depletion layer continues to widen as a function of the magnitude of the gate bias and drives the capacitance even lower. These different regimes are shown in Figure 6 figure when measured as a C-V curve.

Figure 6. C-V characteristics of a MOS devices

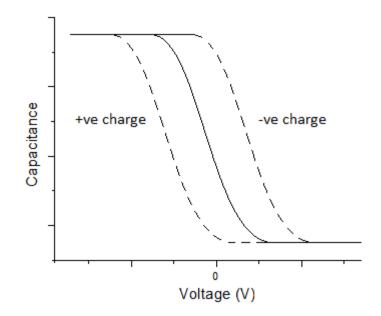

In a real device, there are charges present in the oxide layer and at the interface. These charges can change the C-V measurements. One type of charge is known as fixed oxide charge and these are located near the semiconductor/oxide interface and the effect on the C-V measurements is to translate the graph along the voltage axis but the shape will be unaffected as these charges are not bias dependant. A negative fixed oxide charge will act to shift the measurements to a higher voltage and a positive fixed oxide charge will shift the measurements to a lower voltage. This effect is shown in Figure 7 where the translation along the voltage axis is shown is relation to an ideal device with no fixed oxide charge.

Figure 7. C-V graph showing the effect of fixed oxide charge

This is due to the charges causing band bending at the interface thereby changing the value of  $E_i - E_F$ . A negative fixed oxide charge will increase this value meaning a larger bias is required to move from accumulation to depletion.

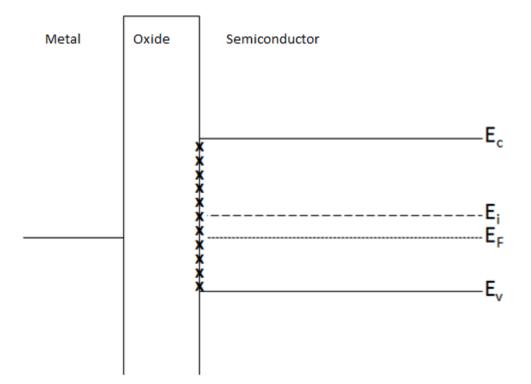

There is another form of charge that is present which is voltage dependant and are known as interface states. These states are present at the interface and their occupation is dependent on their position in the band gap and the position of the Fermi level. Figure 8 shows the position of these states within the band gap.

*Figure 8. Band diagram under flat band conditions where the crosses denote the position of interface states*

There are two kinds of states and these are donor and acceptor like states. Donor like states are neutral when full of electrons and positive when empty. Acceptor like states are negative when occupied with electrons and neutral when empty. As the bias voltage is being swept the band bending at the interface causes these states to fill or empty which changes the overall amount of charge at the interface thereby changing the capacitance being measured. The effect of these interface states on a C-V graph is shown in Figure 9 and the characteristic change in shape known as stretch out.

*Figure 9. CV graph with the dotted line representing the stretch out effect due to interface states*

It is thought that acceptor like states are in the top half of the band gap and donor like states are in the bottom half of the band gap. This means that interface states and fixed oxide charge can be distinguished by measuring at the mid-gap so that all the states are neutral and not contributing to the measurements.

#### 1.2.4 Current Density-Voltage

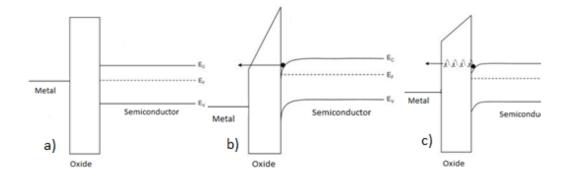

The J-V characteristics of a MOS capacitor are important for determining properties such as the leakage and breakdown voltage of the device. In an ideal device, there would be no leakage current at all but as the insulating layer in the MOS structure is scaled down the leakage due to quantum mechanical tunnelling becomes a constraining issue. The main conduction mechanisms are direct tunnelling, Fowler-Nordheim tunnelling and Frenkel-Poole tunnelling. These different tunnelling mechanisms are shown in Figure 10.

*Figure 10. a) shows the system under flat band condition, b) shows Fowler-Nordheim tunnelling and c) shows Frenkel-Poole tunnelling*

Direct tunnelling occurs due to a finite probability of an electron appearing on the other side of a potential barrier and for thin films this is unavoidable. Fowler-Nordheim tunnelling is where in the presence of an electric field the conduction band of the oxide forms a triangular potential barrier to conduction which can lead to a shortening of the potential barrier and therefore a higher probability of an electron tunnelling through it.

For dielectric layers that are less than about 3.5nm thick direct tunnelling through the layer plays a dominant role whereas for thicker layers in a  $Si/SiO_2$  system Fowler-Nordheim tunnelling plays a larger part and the Fowler-Nordheim conduction is given by

$$J_{FN} = C\xi_{ox}^2 e^{\frac{-\beta(\varphi)}{\xi_{ox}}}$$

Eq.10

where J is the current density,  $\xi_{ox}$  is the electric field,  $\phi$  is the potential barrier height for electron emission and C and  $\beta$  are given by

$$C = \frac{q^3 m_o}{8\pi h m_{ox} \varphi}$$

and  $\beta = \frac{8\pi (2m_{ox})^{\frac{1}{2}}}{3qh} \varphi^{\frac{3}{2}}$  Eq.11

where q is the charge on an electron,  $m_o$  and  $m_{ox}$  are the mass of an electron at rest and the effective mass of an electron in the dielectric respectively and h is Planck's constant.

For high  $\kappa$  dielectrics Frenkel-Poole can contribute more to the leakage current. Frenkel-Poole is a bulk-limited effect which is caused by impurities in the dielectric causing Coulombic traps in the band gap of the dielectric. This means that electrons can hop from trap to trap via the conduction band of the dielectric. The governing equations for Frenkel-Poole conduction given in by

$$J = \sigma_o E e^{B(\xi)^{\frac{1}{2}}} \quad where \quad B = \frac{q}{kT} \left(\frac{q}{\pi \varepsilon_0 \varepsilon_r}\right)^{\frac{1}{2}}$$

Eq.12

where  $\sigma_o$  is the conductivity, T is temperature and  $\varepsilon_0$  and  $\varepsilon_r$  are the permittivity of free space and the dynamic dielectric constant respectively.

It can be difficult to identify which conduction mechanism is dominant so measuring the conduction at different temperatures can help resolve this due to the higher temperature dependence of Frenkel-Poole conduction when compared to Fowler-Nordheim conduction.

1.3 High-k dielectrics

#### 1.3.1 Dielectric theory

The dielectric is a material that can be polarised by the application of an electric field. This happens by the slight rearrangement of the charges within the material and the macroscopic polarisation is given by

$$P = N_m \alpha_m E$$

Eq.13

Where  $N_m$  is the number density of microscopic polarisation,  $\alpha_m$  is the microscopic polarisibility and E is the local electric field.

The Clausius-Mossetti relation is given by [5]

$$\frac{k-1}{k+2} = \frac{4\pi}{3} \frac{\alpha_m}{V_m}$$

Eq.14

Where k is the relative permittivity and  $V_m$  is the molar volume of the system.

From this the macroscopically defined dielectric constant is related to the microscopic polarisation.

The polarisability of a material occurs typically through three different ways, the permanent, ionic and electronic polarisations. It is assumed that there is no permanent polarisation in high-k materials and the dominant polarisation mechanism is via ionic polarisation.

1.3.2 Choice of High-k

There are many options to choose from as a high- $\kappa$  dielectric and some of these are listed in Table 1.

|                                | Dielectric Constant | Band Gap (eV) |  |

|--------------------------------|---------------------|---------------|--|

| SiO <sub>2</sub>               | 3.9                 | 9             |  |

| GeO <sub>2</sub>               | 5-7                 | 5.8           |  |

| Al <sub>2</sub> O <sub>3</sub> | 8                   | 6.4           |  |

| HfO <sub>2</sub>               | 18-25               | 5.8           |  |

| HfSiO₄                         | 11                  | 6.5           |  |

| ZeO <sub>2</sub>               | 25                  | 5.8           |  |

| TiO <sub>2</sub>               | 36-70               | 3.1           |  |

| La <sub>2</sub> O <sub>3</sub> | 30                  | 6             |  |

Table 1. Potential high-k oxides with their corresponding dielectric constant and bandgap

Some of the key requirements of this dielectric for use in a MOSFET are as follows:

1. It must be insulating by having band offsets to the semiconductor greater than 1eV

2. The dielectric constant must be sufficiently high so that it can be used for several scaling nodes

3. It needs to be thermodynamically stable to withstand high processing temperatures during manufacture

4. It needs to form low defect electrical interfaces with the semiconductor and the metal

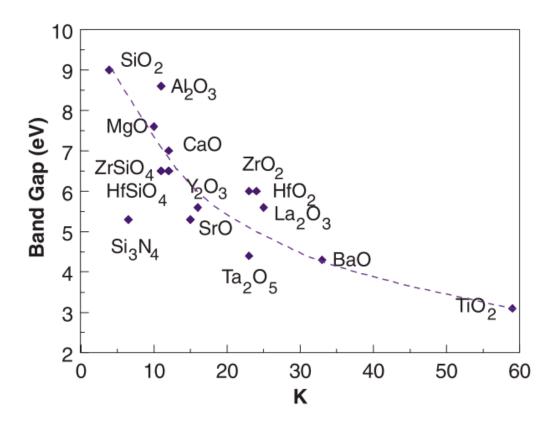

The dielectric constant has an inverse relationship with band gap as shown in Figure 11 so that the materials with a very high dielectric constant are not suitable due to small band offsets. This discounts the very high  $\kappa$  materials such as SrTiO<sub>3</sub> which has a dielectric constant of ~2000 but a band gap of only 3.2 and also TiO<sub>2</sub>[6].

1.4 High Mobility MOSFET Channels

## 1.4.1 Why are they Necessary?

If the silicon oxide layer is being replaced, then the main advantage of using silicon is now less relevant so this means that the channel material can be replaced by one with better electrical properties.

Figure 11. Band gap against dielectric constant, from [7]

The drain current is the current that flows from the source to the drain of a MOSFET and is given by

$$I_D = \frac{W}{L} \mu C_{ox} (V_G - V_T) V_D$$

Eq.15

where W is the channel width, L is the channel length,  $\mu$  is the channel mobility,  $C_{ox}$  is the oxide capacitance,  $V_G$  is the gate voltage,  $V_T$  is the threshold voltage and  $V_D$  is the drain voltage. Increasing  $I_D$  is necessary for improving the device performance. As the terms on the right-hand side of the equation are reduced the drain current will also reduce meaning that the voltages will have

to be increased. This is undesirable for efficiency reasons so increasing the mobility of the channel increases the drain current so that lower voltages can still be used.

## 1.4.2 Channel Materials

One candidate material for use as the channel is germanium due to its superior electron and hole mobilities (2x and 4x larger than silicon respectively). It is also possible that MOSFETs using germanium for the p-type channel due to its large hole mobility and a III-V semiconductor (such as GaAs) for n-type channel due to their high electron mobility will be integrated on the same integrated circuit. The properties of candidate MOSFET channel materials are shown in Table 2.

|                                                        | Silicon               | Germanium            | GaAs                 |

|--------------------------------------------------------|-----------------------|----------------------|----------------------|

| Band Gap (eV)                                          | 1.12                  | 0.66                 | 1.42                 |

| Electron mobility (cm <sup>2</sup> /Vs)                | 1500                  | 3900                 | 8500                 |

| Hole Mobility (cm²/Vs)                                 | 475                   | 1900                 | 450                  |

| Intrinsic Carrier<br>Concentration (cm <sup>-3</sup> ) | 1.45x10 <sup>10</sup> | 2.4x10 <sup>13</sup> | 1.79x10 <sup>6</sup> |

Table 2. Comparison of some of the properties of Si, Ge and GaAs

#### 1.5 Literature Review

For the proper operation of a MOSFET the interface between the semiconductor and the dielectric needs to have a low number of defects and this is referred to as surface passivation. To achieve a well passivated surface a thin passivation layer is required to make a good electrical contact between the germanium substrate and the dielectric as high k dielectrics such as  $HfO_2$  in direct contact with the germanium have a high  $D_{it}$  [8]–[10] so are unsuitable for CMOS applications. GeO<sub>2</sub> can be used to pacify the surface of germanium and a review of the problems associated with it and possible solutions will now be discussed. It was initially thought that a problem with employing  $GeO_2$  as the passivation layer was problematic because the GeO<sub>2</sub> layer would degrade in to its sub oxides [10]. A Ge/GeO<sub>2</sub> interface was shown to have improved electrical properties when the Ge surface was oxidised at a high pressure (70 atmospheres) [11]. This improvement in the interface was explained by considering GeO is formed at the Ge/GeO<sub>2</sub> interface and then diffuses through the  $GeO_2$  and then desorbs at the  $GeO_2$  surface. When the oxygen pressure in increased the vapour pressure of the GeO at the surface is reduced thereby suppressing the desorption of GeO. These MOS capacitors showed a significant improvement of electrical properties when compared to  $Ge/GeO_2$  MOS capacitors grown with atmospheric oxygen and had a minimum D<sub>it</sub> of  $2x10^{11}eV^{-1}cm^{-2}$ . The thickness of the film was 18.5nm which is too thick to be used in advanced CMOS devices as the EOT is too large.

42

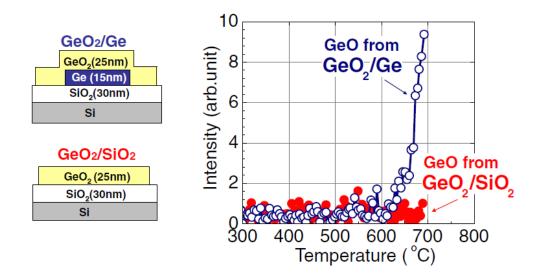

This mechanism for GeO desorption at the interface by the reaction of Ge and GeO<sub>2</sub> was confirmed by Kita et al who sputtered GeO<sub>2</sub> on to Ge and on Si [12]. These films were then annealed at various temperatures and thermal desorption spectroscopy (TDS) was used to analyse the desorbed species. Figure 12 shows the results of the TDS analysis.

Figure 12. A schematic (left) of the gate stacks fabricated for TDS analysis. The results of the TDS are shown on the right, after Kita et al [12]

The intensity of the signal above 600°C increases for the Ge/GeO<sub>2</sub> system but not the SiO<sub>2</sub>/GeO<sub>2</sub> system. The authors conclude that the GeO desorption is driven by the reaction at the interface between Ge and GeO<sub>2</sub> and not from the bulk of the GeO<sub>2</sub> otherwise there would be a GeO signal from both sets of samples. Oniki et al performed similar experiments and also found this desorption of GeO from the interface but with the onset of desorption occurring at a lower temperature of around 400°C [13]. Milojevic et al investigated how the Ge surface changes during an ALD process [14]. This was achieved by interrupting the ALD process in between pulses and then employing in situ XPS analysis. Figure 13 shows the XPS data for deionised water (DIW) etched Ge surface and how it evolves with processing and a Ge surface cleaned by UHV annealing.

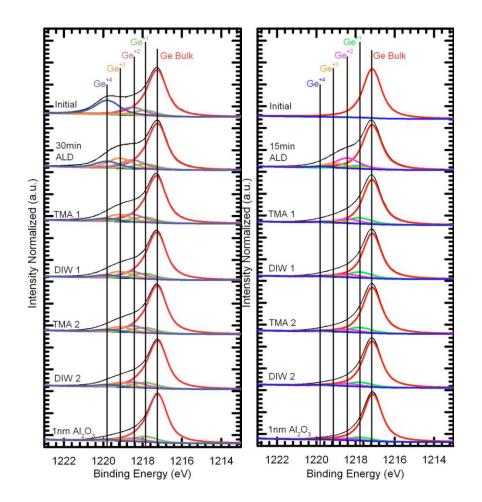

Figure 13. XRD spectrum showing Ge  $2p_{3/2}$  of DIW etched germanium (left) and UHV cleaned germanium (right) showing reduction in the germanium oxides after TMA and water pulses. After Milojevic et al [14]

These results show that the surface is very sensitive to the ambient condition in the ALD reactor as after 15 minutes the "clean" Ge grows a thin oxide in the reactor which is then reduced upon successive ALD cycles of TMA and H<sub>2</sub>O. DIW etched Ge showed a reduction in the initial oxide surface and a shift to lower oxidation states which were then reduced during the ALD process. These results highlight the difficulty in processing as this initial oxidation will always be present in a commercial ALD tool.

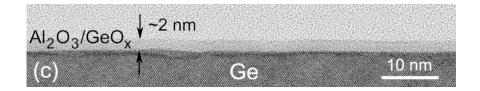

$Al_2O_3$  has been proposed as a barrier against the desorption of GeO. Zhang et al [15] proposed a method whereby a Ge/Al<sub>2</sub>O<sub>3</sub> gate stack was grown by ALD and subsequently given an electron cyclotron resonance (ECR) plasma post oxidation resulting in a Ge/GeO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> gate stack. Figure 14 shows a TEM image of the resulting gate stack.

Figure 14. TEM image of a  $Ge/GeO_x/Al_2O_3$  gate stack, after Zhang et al [15]

The thickness of  $Al_2O_3$  was 1nm and after the oxygen plasma treatment the film grew to 2nm. The lack of clarity between the  $GeO_x$  and  $Al_2O_3$  was attributed to low contrast in the TEM image between the two layers and that they are extremely small (~1nm). The MOS capacitors showed improved C-V

characteristics after the plasma treatment and had a  $D_{it}$  of  $5x10^{10}eV^{-1}cm^{-2}$  for p-type and  $6x10^{10}eV^{-1}cm^{-2}$  for n-type. Subsequent investigations from the same group [16] showed that the  $D_{it}$  has a strong dependence on the thickness of the GeO<sub>x</sub> layer which is showed in Figure 15 where the differing thicknesses of the GeO<sub>x</sub> was achieved by keeping the plasma treatment the same but changing the thickness of the Al<sub>2</sub>O<sub>3</sub> layer. The thicker Al<sub>2</sub>O<sub>3</sub> layers reducing the amount of active oxygen species available to form GeO<sub>x</sub>.

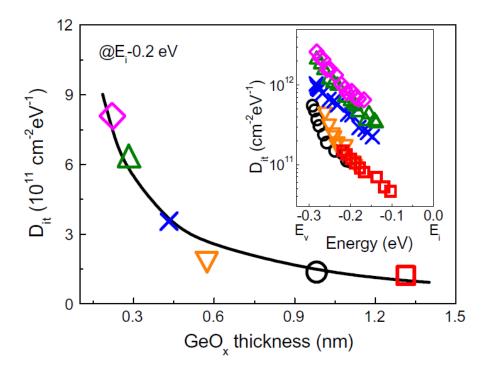

Figure 15. *D<sub>it</sub>* at -0.2eV as a function of GeO<sub>x</sub> thickness with the corresponding *D<sub>it</sub>* distributions in the inset, after Zhang et al [16]

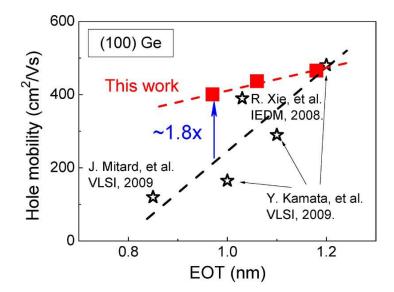

This shows that if the thickness of the  $GeO_x$  layer is less than 0.5nm then the  $D_{it}$  rises sharply. Using this manufacturing technique to make pMOSFETs the hole mobility was characterised as a function of EOT and is shown in Figure 16.

Figure 16. Peak hole mobility as a function of EOT of the pMOSFETs fabricated in [17] compared with other work in the area, after Zhang et al [17]

More recent work used the same technique but this time as a  $Ge/GeO_x/Al_2O_3/HfO_2$  gate stack so that the thickness of  $Al_2O_3$  could be reduced making it possible to scale down the EOT of the gate stacks. Figure 17 shows how the EOT can be reduced using this tri-layer gate stack whilst maintaining a low  $D_{it}$ .

The electron and hole mobilities were also characterised as the plasma oxidation time was varied giving different thicknesses of  $GeO_x$  and are shown in Figure 18 [17]. The samples had 2.2nm HfO<sub>2</sub> and 0.2nm Al<sub>2</sub>O<sub>3</sub> deposited by ALD with different EOT values corresponding to the different thicknesses of the underlying  $GeO_x$ .

Figure 17.  $D_{it}$  as a function of EOT for gate stacks with and without using  $HfO_2$  for lowering the EOT, after [17]

Figure 18. Ge p and n-type MOSFETs giving the hole (a) and electron (b) mobilities for  $Ge/GeO_x/Al_2O_3/HfO_2$  gate stacks, after Zhang et al [17]

These MOSFETs showed a peak hole mobility of 596cm<sup>2</sup>/Vs and peak electron mobility of 754cm<sup>2</sup>/Vs. The authors conclude that these results show the feasibility of applying this technique in high performance CMOS.

One possible route towards creating a gate stack with a low EOT and low  $D_{it}$  is to use sulphur to passivate the germanium surface. Merckling et al [18] proposed a method whereby the germanium substrate was heated up to 750°C in a UHV environment to evaporate the surface GeO<sub>2</sub>. This surface was exposed to molecular H<sub>2</sub>S at a pressure of 2x10<sup>-6</sup> Torr and underwent subsequent deposition of Al<sub>2</sub>O<sub>3</sub> by MBE. Structures with an ultrathin Al interlayer between the H<sub>2</sub>S and the Al<sub>2</sub>O<sub>3</sub> layers were also fabricated. MOS capacitors were used to characterise the interface after forming gas annealing and the C-V measurements are shown in figure 1.

Figure 19. CV characteristics as a function of frequency of  $Al_2O_3/H_2S$ —Ge (left) and  $Al_2O_3/Al/H_2S$ —Ge (right) MOS capacitors measured at RT, after Merckling et al [18]

These show a characteristic C-V curve with very low frequency dispersion in accumulation. In the strong inversion region, the frequency dispersion was attributed to the fast response of minority carriers in the Ge. For the Al<sub>2</sub>O<sub>3</sub>/H<sub>2</sub>S–Ge system, the interfacial state D<sub>it</sub> values were extracted using the conductance method and estimated to be 5 x  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. In the case of the Al<sub>2</sub>O<sub>3</sub>/Al/H<sub>2</sub>S–Ge system, the interfacial state D<sub>it</sub> values were estimated to be low  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. The authors assert that the use of an interfacial Al pre-layer has evidently improved the electrical passivation.

Another method of fabricating S-passivated Ge gate stacks is to expose the surface of HF cleaned germanium to ammonium sulphide ex situ. Sioncke et al used this method with subsequent high-k deposition via ALD [19]. Figure 20 shows the CV characteristics of Ge/S/Al<sub>2</sub>O<sub>3</sub> (8nm).

Figure 20. CV as a function of frequency characteristics of  $Ge/S/Al_2O_3$  (8nm) with p-type (left) and n-type (right) Ge, after Sioncke et al [19]

Figure 21 shows the  $D_{it}$  distribution as a function of position in the band gap for this Ge/S/Al<sub>2</sub>O<sub>3</sub> (8nm) system.

Figure 21.  $D_{it}$  distribution as a function of position in the band gap for a Ge/S/Al<sub>2</sub>O<sub>3</sub> (8nm) gate stack, after Sioncke et al [19]

As this gate stack has a low D<sub>it</sub> at the valance band edge it is most suitable for PMOS operation. Gate stacks were also fabricated with HfO<sub>2</sub> and ZrO<sub>2</sub>. Figure 22 shows the C-V characteristics for these gate stacks which show that the use of high-k in direct contact with the S-passivated Ge have strongly degraded C-V behaviour.

Figure 22. CV as a function of frequency characteristics of Ge/S/ZrO<sub>2</sub> (8nm) on p-type (A) and n-type (B) Ge. Ge/S/HfO<sub>2</sub> (4nm) on p-type (C) and n-type (D) are also shown, after Sioncke et al [19]

The authors conclude that a bilayer structure with at least 2nm of  $Al_2O_3$  with high-k on top is the best route towards structures low  $D_{it}$  and scaled down EOT.

Chellappan et al [20] have performed an XPS study of S-passivated Ge which was achieved by immersion in ammonium sulphide for 20 minutes at room temperature with subsequent deposition of Al<sub>2</sub>O<sub>3</sub> by ALD using TMA and H<sub>2</sub>O as the precursors. Figure 23 shows the Ge 3d XPS spectra of Ge/S/Al<sub>2</sub>O<sub>3</sub> and how it varies with anneal temperature.

Figure 23. XPS spectrum showing Ge 3d spectre of a Ge/S/Al<sub>2</sub>O<sub>3</sub> sample after successive anneal cycles, after Challapan et al [20]

The authors estimate that the oxide component is 0.7nm thick and shows significant reduction upon annealing up to 600°C where it is totally removed and a small new peak 0.53eV below the main peak appears which is attributed to the creation of germanium dangling bonds at the interface. The authors used Kraut's method to calculate the band offsets of the structure after the 600°C anneal and found the valance band offset to be 3.4eV and the conduction band offset to be 2.74eV and conclude that these offsets are an effective barrier against carrier injection across a MOS device.

The same group also performed an XPS study of  $HfO_2$  on S-passivated Ge [21]. Figure 24 shows the thermal stability of the Ge-S bond.

Figure 24. XPS spectrum showing Ge 3d peak and S 2p peak (inset) for S-passivated Ge at various temperatures, After Challappen et al [21]

These results show that the sulphur signal shows no change up to 400°C and decreased to below the detection limit after 600°C annealing. The authors also find that after the sulphur treatment there are no germanium oxide components in the Ge 3d peak profile but after ALD of HfO<sub>2</sub> there is a 1nm thick interfacial oxide which forms either during deposition or following air exposure. The band offsets were also calculated with the valence band offset

as 2.7eV and the conduction band offset as 2.3eV which is sufficient to act as a barrier against carrier injection across a MOS device.

A study by Fleischmann et al [22] shows that the ammonium sulphide treatment saturates after 30s with a maximum sulphur coverage below half a monolayer and that the Ge-S bonds are preserved upon moderate exposure to ambient conditions and after ~2 hours approximately 15% of the sulphur is oxidised from which they conclude that proper control of the time exposed to ambient conditions is crucial to prevent degradation of the surface properties and the electrical performance loss that could be associated with it. Figure 25 shows a XPS spectra of the Ge  $2p_{3/2}$  spectre from this study.

Figure 25. XPS spectrum showing Ge  $2p_{3/2}$  with HF cleaned Ge, S treated Ge and an untreated GeO<sub>2</sub>/Ge sample. The inset shows a close up of the maximum intensity, After [22]

There is an increase in binding energy of 0.13eV after S-treatment. This coupled with scanning tunnelling spectroscopy (STS) data from the authors shows that the Ge-S have a partial ionic character causing band bending at the interface and a depletion of the majority charge carriers near the surface of the germanium.

Other passivation methods have been used to lower the  $D_{it}$  but these have not quite as low as the GeO<sub>2</sub> case. These include nitridation of the germanium surface to form either GeN<sub>x</sub> or a GeO<sub>x</sub>N<sub>y</sub> layer [23]–[29]. These passivation layers are made by plasma nitridation [26], [28], [29] and NH3 exposure [30]. It has been reported that the  $D_{it}$  is larger for these devices than a germanium oxide interfacial layer [31].

#### 2. Growth and Processing

## 2.1 Germanium Substrate Cleaning

An important part of the process when trying to achieve low EOT's is the correct cleaning of the substrate so as to remove all of the native germanium oxide which has a low  $\kappa$  value (4.5-7 depending on growth conditions). There are many ways in which this cleaning can be achieved, e.g. HF [32]–[36], HCl [32], [33], [37], HBr [33], [36], [37], using H<sub>2</sub>O<sub>2</sub> as an intermediate step [33], [38]. Cyclic HF cleaning is the most commonly used and the hydrogen coverage of the surface of the germanium is proportional to the concentration of the HF [32]. Using a cyclic  $H_2O/H_2O_2$  (30%)/HF(10%) procedure with nitrogen drying in between each step, Rivillon et al [39] reported an oxide free fully hydrogen terminated surface but has large carbon contamination when exposed to ambient air. Others have reported a small amount of native oxide remaining after HF cleaning [36] but this is often removed by annealing in a vacuum or in a hydrogen environment which removes any carbon contamination associated with the HF clean. HBr cleaning gives a fully bromine terminated surface but upon exposure to  $H_2O$  the Ge-Ge back bonds break and then replace the halogen terminated surface with a hydroxyl group which then leaves the surface prone to oxidation in the presence of oxygen [37] and this process occurs for chlorine terminated surfaces as well. As germanium oxide is volatile

at temperatures above 430°C, annealing in a UHV will cause the native oxide layer to desorb from the surface leaving an oxide free surface [9].

For this work the most repeatable method for wet cleaning was found to be a three-minute ultrasonic bath in acetone to degrease the surface followed by a 30s dip in DI water to etch most of the native oxide. This was then followed by exposure to oxygen plasma in the ALD chamber to grow a sacrificial oxide which was then subsequently etched by cyclic HF/DI water rinses. This method was found to be the most consistent at etching the native oxide as other methods would sometimes not uniformly etch across the whole sample when measured by ellipsometry at various points across the sample. If the acetone step is missed, then sometimes the HF dips don't etch the surface at all meaning that this step is important for consistent etching results.

# 2.2 Atomic Layer Deposition

#### 2.2.1 The ALD Process

Atomic layer deposition is similar to chemical vapour deposition but the film is achieved by a sequential, self-saturating reaction. The method was first used for commercial use by Suntola et al [40] in the 1970's and was then known as atomic layer epitaxy. This use was for creating uniform thin films for use in Thin Film Electroluminescent Displays. The process has since become of great interest to the semiconductor industry due to the very desirable properties of the films.

It was then later popularised in the semiconductor industry in DRAM fabrication and later when in 2007 it was used for the deposition of the high-k/metal gate stack for microprocessors [41].

These films can be made to be very thin due to the layer by layer approach that the technique uses, the films are highly conformal and pin-hole free.

The basic operating principle is that the substrate (germanium in these experiments) is exposed to a gaseous precursor which reacts with the surface of the substrate in a self-limiting way, i.e. it reacts with every available surface site on the substrate and then stops reacting because the precursor is specially chosen so that it does not react with itself (Figure 26a). The remaining precursor is then purged out of the chamber (Figure 26b). Once all the initial precursor is out, another gaseous chemical is introduced to the chamber (often water) and this then reacts with the new surface on the substrate, again in a self-limiting way so as to create a stable monolayer (e.g. HfO<sub>2</sub>) on top of the substrate (Figure 26c). This second chemical is then purged out of the chamber (Figure 26d) and the resulting surface is accommodating to a reaction with the initial precursor which means that the reaction can be repeated so that one monolayer can be deposited at a time giving great control of the

59

thickness of the film. A schematic illustration of this process is given in Figure 26.

Figure 26. The sequential nature of ALD schematic with a) precursor 1 pulse, b) purge, c) precursor 2 pulse and d) purge leaving a deposited monolayer

This control of the deposition rate gives many advantages over other deposition technologies. The film has a very high degree of conformity due to the fact that the process is self-terminating which means that it can be used for structured surfaces (e.g. trenches). The nature of the process makes it pinhole free which is advantageous for passivation layers and dielectrics. The process is very repeatable and can be scaled up relatively easily which is why it has become used in manufacturing. The single monolayer deposition per cycle is an ideal case and usually does not happen and the deposition is only a fraction of a monolayer per cycle. The main reason for this is steric hindrance which is where active surface sites are obscured from the reactive precursors by the ligands of adjacent reacted precursor molecules.

The choice of precursors is very important and there are some precursor properties that are essential for ALD growth. The precursors must be volatile because the precursors are delivered to the substrate in the vapour phase. If the precursor has insufficient volatility at room temperature, then it needs to be heated but not to the extent that the precursor thermally decomposes which is one of the reasons that precursor choice and the processing conditions are so important so that high quality films can be fabricated. If the precursor is too thermally unstable then decomposition can occur at the substrate causing impurities in the film which will degrade the film properties. If the precursor is volatile, then the precursor can be delivered to the chamber by vapour draw where the valve to the precursor is opened and the pressure of the precursor means that it will readily come out of the bubbler in a vapour and flow to the chamber. If the precursor is less volatile, then it should be bubbled. This means that the pot containing the precursor has a dip leg in it which an inert gas such as argon flows through. This gas then flows through the precursor and out of the pot into the chamber and it picks up some of the

precursor with it and delivers it to the chamber. The different growth mechanisms are shown in Figure 27.

# Substrate temperature

Figure 27. ALD growth rate against substrate temperature

If the temperature is too low, then two things can happen:

1. The growth rate is less than expected due to there not being enough surface energy to facilitate to reaction.

2. The growth rate is more than expected due to the precursor condensing on the substrate

There is then a region known as the ALD window where the growth rate remains constant with increasing substrate temperature which is characteristic of the self-limiting nature of ALD. If the substrate temperature is further increased, then two things can happen:

1. The growth rate rises which is caused by the thermal decomposition of the precursor so therefore causes impurities in the film.

2. The growth rate falls as the precursor desorbs from the surface which makes the process no longer saturative so more cycles are necessary to reach a desired thickness.

The purge time is also an important part of the ALD process as if insufficient time is allowed for all the previous precursor to be removed from the chamber then the next precursor pulse could react with any remaining precursor causing a CVD like reaction allowing less control of the growth rate.

The hafnium precursor used in this study for HfO<sub>2</sub> deposition was (MeCp)<sub>2</sub>Hf(OMe)(Me) due to Cp (cyclopentadienyl) based precursors having good thermal stability and low levels of impurities [42]. The precursor bubbler was set to 100°C. Titanium isoproproxide was used as a precursor for TiO<sub>2</sub> deposition due to its extensive use in industry. The bubbler was set to 50°C. Trimethyl Aluminium was used for Al<sub>2</sub>O<sub>3</sub> as this is extensively used precursor so is the standard for depositions using aluminium.

63

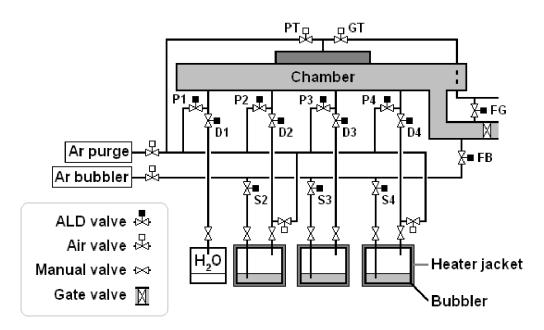

## 2.2.2 The Opal Reactor

These studies use an Oxford Instruments OpAL reactor for ALD depositions and a schematic of the OpAL reactor is shown in Figure 28 [43].

Figure 28. OpAL reactor schematic [43]

## 2.2.3 Thermal Deposition of Oxides

H<sub>2</sub>O can be used as the oxidising species in ALD. As H<sub>2</sub>O has a high vapour pressure it can be delivered by vapour draw. The pulse time for TMA was 0.01s and the water pulse was 0.03s and vapour draw was used as the vapour pressure was high enough that bubbling was unnecessary. Both the (MeCp)<sub>2</sub>Hf(OMe)(Me) and titanium isoproproxide were bubbled using argon and the pulse was for 3s.

#### 2.2.4 Plasma Enhanced Deposition of Oxides

Another way of delivering oxygen to the film is to use an oxygen plasma. The OpAL reactor uses a remote inductively coupled plasma in a downstream configuration. This is used as it has been reported that films that are grown where the substrate is immersed in the plasma have high levels of plasma induced damage making this method unsuitable for delicate microelectronics where this damage would impact device performance. By using a remote plasma this plasma induced damage is reduced so that it can be used as a method for depositing layers within delicate structures. The oxygen plasma used was at 300W with 60sccm of O<sub>2</sub> flowing for 3s.

## 2.3 Molecular Beam Epitaxy

MBE is a deposition technique that can achieve very pure and conformal thin films with monolayer resolution and a high degree of control over doping or composition. It is widely used in industry due to its desirable film deposition properties.

MBE uses very pure material sources (e.g. AI) and then heats the source until they slowly sublime. A shutter is placed in front of the source before deposition and the MBE system needs to have an ultra-high vacuum (UHV) because the material being deposited, in this case AI, will be arriving at the target substrate in atomic form and therefore needs a long mean free path so

65

that it does not interact with any impurities in the chamber. Once the substrate is in the chamber and the requisite vacuum level has been reached the shutter on the Al source is opened for however long is necessary for a certain thickness (typical growth rates are Å/s). This growth is often measured in situ by RHEED analysis so that atomic control of thickness can be attained. MBE was used in this research so that germanium wafers could be cleaned by heating the germanium in UHV leaving an oxide free surface which then had Al metal deposited to try and avoid regrowth of GeO<sub>x</sub> when transferring to the ALD reactor ex situ.

#### 2.4 Metal Gate and Back Contact Deposition

To reduce the series resistance of the MOS structure the back of the wafer is coated in Al. First the back is scratched using a diamond scribe and then aluminium is deposited by thermal evaporation to create an ohmic contact. This is performed otherwise the electrical characterisations are effected by essentially having another capacitor in series on the back of the substrate which also creates series resistance. The top gate contact of the MOS device was formed either by evaporating or sputtering of gold through a shadow mask.

2.5 Physical Characterisation

## 2.5.1 Ellipsometry

66